太阳诱电在2010年10月5日开幕的“CEATEC 2010”上,参考展出了可重构LSI“MPLD(Memory-based Programmable Logic Device)”的技术详情。MPLD采用元件呈阵列状排列7输入7输出“MLUT(multi-LUT)”的构成方式。元件间通过MLUT连接在一起。和普通的FPGA一样,MPLD元件无需开关,具有元件构造简单、可减小芯片面积的特点。太阳诱电在2009年的CEATEC上首次公开了MPLD,但并未公开元件构成等技术详情。

一般情况下,FPGA的LUT输入数比输出数多,太阳诱电的MPLD元件(MLUT)则为7输入7输出,输入数与输出数相同。这样做不仅可使元件作为逻辑栅极使用,还可将其用于替代布线及开关的用途。布线较多的电路与栅极较多的电路等即使混载在一起,MLUT本身也可用于这两方面用途,具有可灵活应用的特点。

普通FPGA的LUT与开关数量的比例是固定的,比如,布线较多的电路很可能出现开关数量不足的情况。“MPLD采用了类似于从FPGA中拆除开关的构成方式”(开发伙伴广岛市立大学研究生院教授弘中哲夫)。与FPGA的基本构成不同,因此不触犯FPGA的基本专利。

工作频率为200MHz左右

将元件用于布线的构思以前就存在于可重构LSI领域。一般情况下,利用元件将布线连接在一起后,会出现延迟时间增加、工作频率降低等问题。而MPLD通过设置除了近距离元件之间外,还可连接远距离元件的“间隔布线”,控制了工作频率的下降。虽然还取决于用户电路的构成,但“如果电路极其简易,在200MHz左右频率下即可工作”(该公司开发研究所技术企划部主任研究院石黑隆)。据太阳诱电介绍,在间隔布线上,跨越元件的数量“目前不足10个”,详细数值目前仍在研究。关于触发器(Flip Flop),目前已安装在一半左右的元件上。

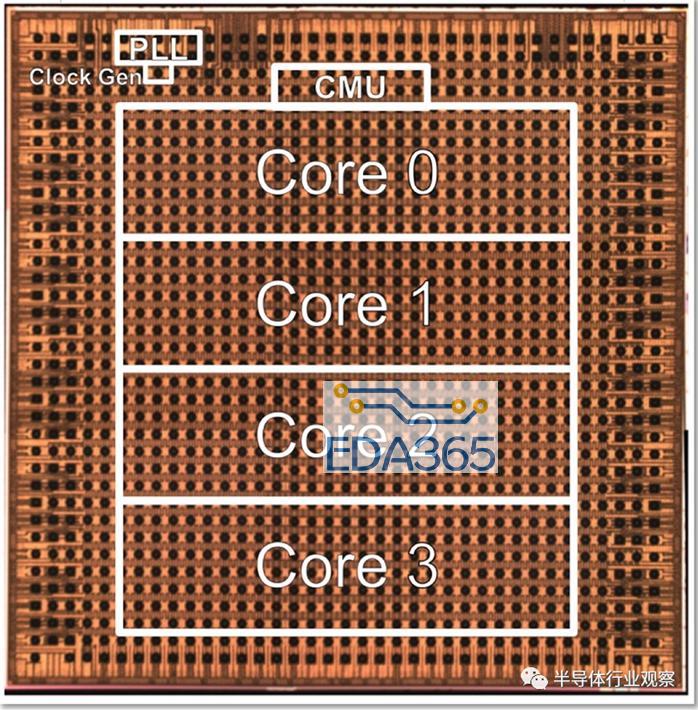

作为MPLD的首批元件,名为“SoCR”的LSI预定2010年12月前后开始样品供货。SoCR是指在MPLD上追加CPU内核,可替代SoC使用的元件。MPLD以双插槽构成的形式配备了21×30个元件。由于采用双插槽构成,因此一个工作时,通过改写另一个的电路构成,可实现动态可重构性。

此次的SoCR采用0.18μm的CMOS技术制造。耗电量为数百mW以下。可在MPLD上安装的电路规模方面,1个元件相当于最多30~35个栅极,整个SoCR可安装约20个8bit的乘法器。

利用C语言输入

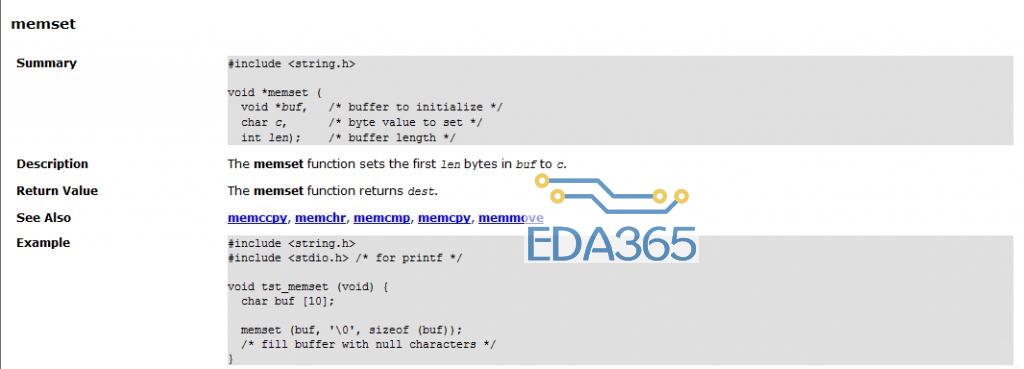

MPLD用设计工具“MPLD Designer”预定与样品芯片一道于2010年12月前后提供。可利用C语言输入,还支持Verilog-HDL输入。利用C语言设计时,运算器的bit宽度等利用C语言的注释指定。外部的IP内核作为宏利用时,也可通过注释指定。配置布线的结果可通过“MPLD Viewer”在GUI上确认。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多