在国际测试大会上,英特尔公司副总裁兼副总经理Gadi Singer在题为“应对频谱纳米技术和千兆复杂性的挑战”的演讲中指出,从1940年以来,每立方英尺MIPS或每磅MIPS数每10年就增加100倍。虽然在平滑的曲线上一直是以指数规律变化,但是,在那个时期仍然有许多不连续性和变形点。

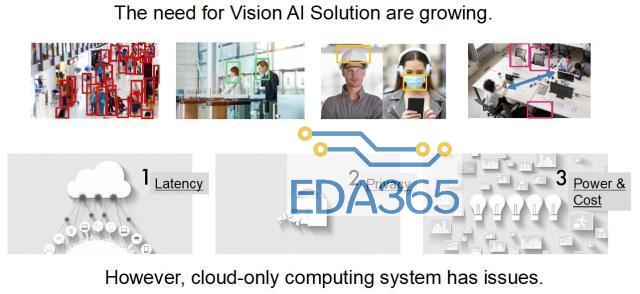

“目前,四个不同的趋势正延伸在所有方向中的曲线,”Singer说道。首先,IC复杂性和多样性正受到智能(便携式)设备的出现的驱使。这些新的设计包含复杂的内核、多处理引擎、更多的存储区、专用的子系统以及在片上的多个通信系统。此外,Singer表示,“互联网的影响”证明数字数据的融合的影响渗透到了所有的功能之中,并且需要增加硬件和软件的互动。”

显然,Singer表示,这种下一代系统级芯片需要在测试开发工具和技术上做出改进。扫描方法存在速度问题,并且正在接近极限。功能测试方法的自动化程度不够,并且不成标准。内建自测试(BIST)对于存储器测试而言模式有限,而逻辑BIST随着芯片面积的增加而越来越昂贵。改进这种状况的唯一办法就是:让一种针对X方法的集成设计—X指的是测试、制造、良率及可靠性与即插即用的模块性、可配置性以及针对所有IP模块的可修改测试解决方案结合起来。

其次,功耗和性能正在朝着更低功耗和固定的预算迈进。“下一代芯片”他补充说,“将需要在恒定的功率封包内展示更多的性能,而设计变量将必须适合不同的功率预算。”针对功率的测试和针对性能的保护在一定的功率级将是至关重要的。遗憾的是,该行业需要的解决方案比现有的解决方案还要多,因为测试将必须解决功率测试、在速功率测试以及作为电池寿命中因子的在工作负载测试。

第三个领域就是纳米科技。摩尔定律可能在可以预见的将来依然有效,即使在缩放技术上的创新将跟材料领域的创新一样多。“即使在测试领域需要更多的创新,”Singer说,缩放导致每个裸片中的三极管和功能的增加,尽管也造成裸片内和裸片间可变性的增加。将来的设计将需要在设计和测试上提高对各种变化的灵敏度,与此同时,IP必须宽容制造可变性。Singer指出,“人们要采用自适应测试方法来解决可变性问题以及由此而来的设计灵敏度问题。”

最后,所有这种挑战性的工作必须在较少的时间内完成,Singer表示,“总的回报时间(TAT)是从设计到原型再到生产转移的关键尺度。短的产品窗口将需要迟约束—取决于在设计周期中最后一分钟的实现细节。”设计正给测试开发能力带来严峻的挑战。半导体行业需要快速和买得起的测试开发能力,以确保末级的重新配置。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多