富士通微电子欧洲(FME)公司和英国Toric公司携手利用Toric获得专利的AJC反抖动单元(Anti-Jitter Cell, AJC)技术实现了对嵌入式抖动压缩宏的验证,近日双方公布了合作成果。

AJC技术为Toric的第一个产品—PhaseFilter—奠定了基础,这是一种压缩时钟信号抖动的低功耗片上电路。

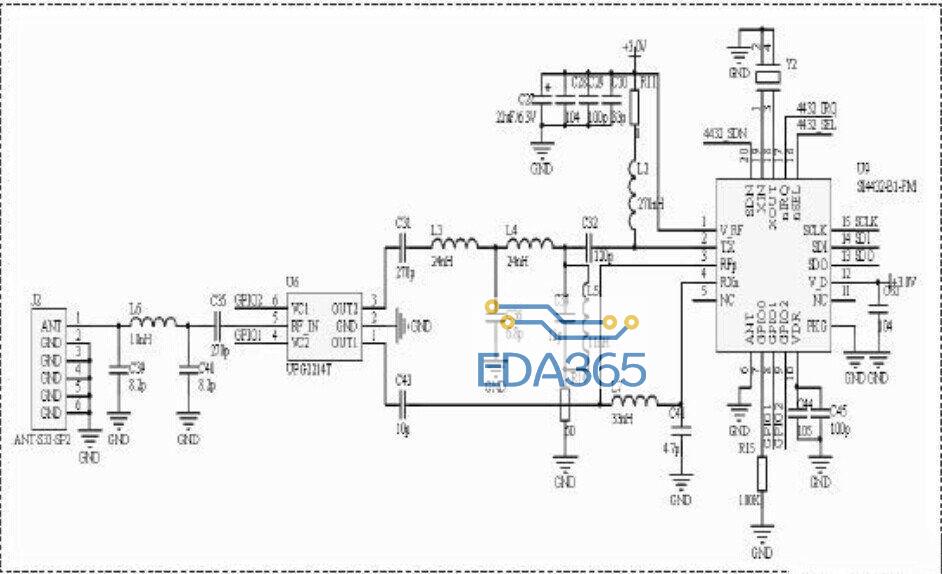

该种设计仅仅采用通用的构建模块,因此能采用广泛系列的半导体工艺实现。利用典型的高级混合信号CMOS工艺,该宏摸块可以实现大于1GHz的工作频率,并具有 2:1 的跟踪范围和-150dBc/Hz稳定噪声(远远低于载波)。

PhaseFilter能增强一系列应用中的IC性能,这些应用包括RF本地振荡器(LO)合成、串行通信和低功耗PLL及数字音频。直接的优越性体现在它使系统的功耗降低,并减少的硅的面积。

“这些令人深刻印象的结果证实了我们的技术在低功耗的PLL和快速高分辨率数据转换器这些应用中的功效,” Toric的研发总裁Mike Underhill教授说,“因为这些领域是FM的‘最佳化方案战略’的核心,他们对我们的技术的信心已经结出了丰硕的成果。”

FME的最新测试芯片以90纳米技术实现,它在500MHz展示了6:1的抖动抑制性能。FME的高级工程总监Neil Amos补充说,“通过在未来的混合信号产品中集成PhaseFilter,Toric的AJC技术的实现是FME这一计划的重要里程碑,它为消费者提供了真正益处。”

通过创建、优化和验证针对抖动抑制的嵌入式宏模块,参考设计和模拟工具使设计工程师能把Toric的AJC技术集成到他们自己的产品当中,从而以低功耗和高的面积利用率来提供高性能。

在2002年,Underhill教授在萨里大学对AJC抖动抑制技术进行了构思,其后Toric从该所大学获得相关的一揽子知识产权,而该所大学也持有Toric的少部分权益。

Toric技术开发的最初阶段是通过英国贸易部连续提供的支持实施的,最初由聪明创新奖支持,后来是由泛欧洲的欧洲尤利卡计划提供支持。所使用的经费最初来自Toric的管理团队,此后来自主要以剑桥为基础或与剑桥有关的‘天使’投资者。Toric是一家私人企业。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多