Zynq最大的优势在于,同时具备软件、硬件、IO可编程,即All Programmable。在设计Zynq过程中,同样要建立一种意识,就是从原来单纯的软件思维(或单纯的硬件思维)中解脱,转向软硬件协同设计的开发方法。

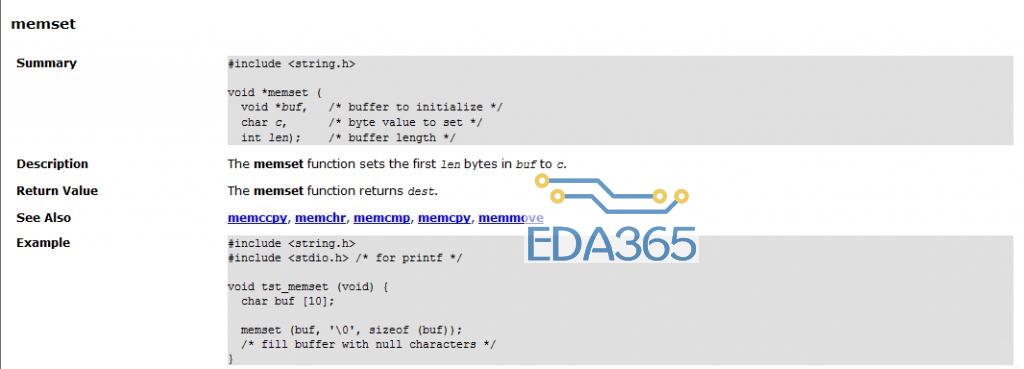

软件设计,即基于ARM的软件开发,我们第三节里面已经做过例子了,基本就是通过某一硬件地址映射寄存器与相应的硬件进行交互,这类硬件包括ARM外设如GPIO,EMIO,SPI,TImer等,也包括挂载到AXI总线上的PL。除此之外,软件还要处理好诸如操作系统、网络等高层任务。

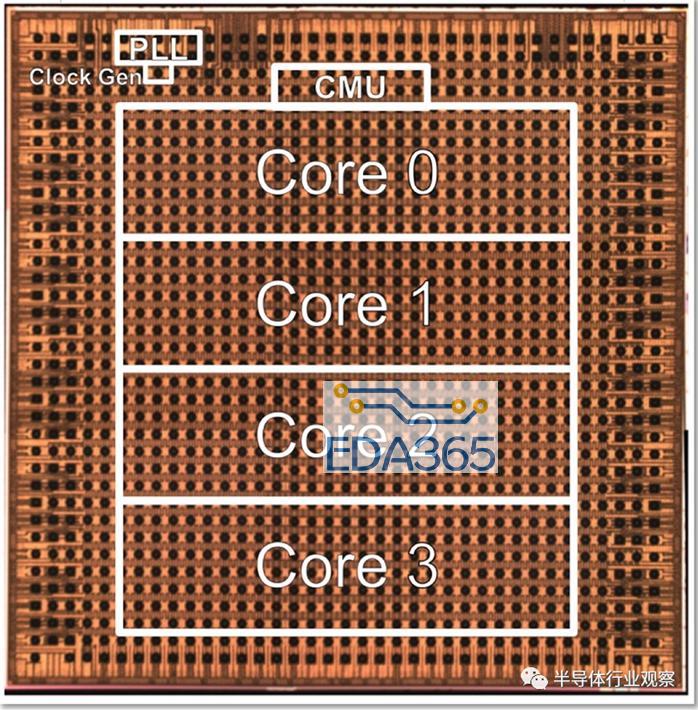

硬件设计,即基于FPGA的逻辑开发,主要通过实例化一些现成的IP,利用状态机实现自身逻辑功能,然后实现AXI接口与ARM进行通信。

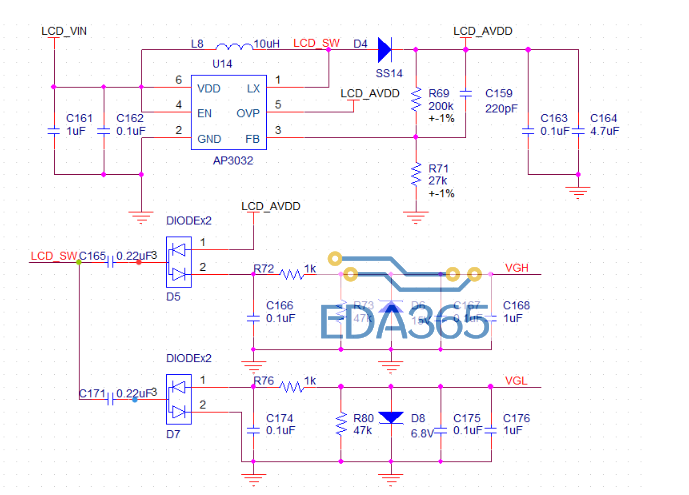

将软硬件结合进行设计,需要AXI总线。我们反复强调了AXI的重要性,可以说它决定了软硬件协同设计的成败。

关于Zynq的网络教程也有很多了,像懒兔子的 ,笔者初学Zynq时是按照他的教程一步步做实验的。本教程不会重复这些步骤,而是帮助初学者建立一个框架,剩下的就是自己通过查文档、做实验去填充这些具体内容。

我们大体划分一下Zynq开发的框架:

首先是需求分析,确定要做什么;之后将任务进行细分,一般可以看哪些适合在FPGA上实现,单独提出;剩下的则用PS。接着选择通信接口,物理链路选择GP或HP或ACP,协议选AXI-Lite,AXI-FIFO或AXI-Stream。划分完毕,则逻辑工程师与ARM工程师从这里分道扬镳,按照各自任务进行实现。

逻辑工程师需要集中精力做IP设计,将功能集成到一个用户IP中,并留出通信接口与AXI通信。

ARM工程师则根据需求建立ARM裸机软件工程或基于嵌入式Linux的工程,前者开发周期较短,后者功能较强但需要为Linux做很多准备工作(引导,内核,文件系统,驱动,图形界面开发等)。虽然基于嵌入式Linux的开发看上去很“酷”,但我们要把握好分寸,能用裸机实现的坚决不用操作系统,否则只会劳民伤财。

各自开发工作完成后,进入联调,ARM通过读写PL映射寄存器来查看相应功能是否正常,如果不正常则需要返工修改,反复测试,直到解决问题为止。

APP下载

APP下载 登录

登录

热门文章

热门文章