基于锗离子注入的硅波导工艺和激光退火工艺,他们实现了可擦除的定向耦合器,进而实现了可编程的硅基集成光路,也就是所谓的光学FPGA。

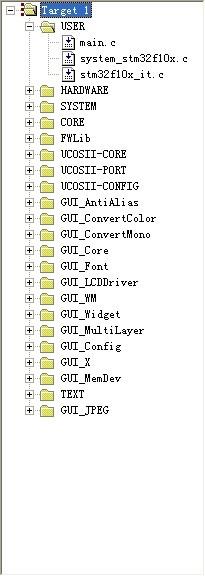

这篇笔记主要分享硅光芯片的一篇最新进展。英国南开普敦大学Reed研究组最近在arXiv贴出了一篇硅光的研究进展 arXiv 1807.01656, “Towards an optical FPGA - Programmable silicon photonic circuits“。基于锗离子注入的硅波导工艺和激光退火工艺,他们实现了可擦除的定向耦合器,进而实现了可编程的硅基集成光路,也就是所谓的光学FPGA。

集成电路中的FPGA(field programmable gate array), 即现场可编程门阵列。FPGA内部是一些基本逻辑单元,工程师可根据需要,将这些逻辑单元按特定的方式连接起来(烧录)。FPGA的功能可根据设计者的需求而改变。其设计周期短,开发费用低,风险较小。

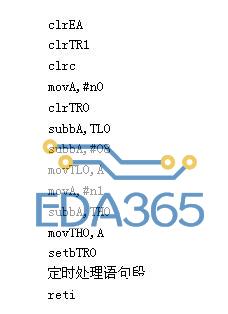

光学FPGA的出发点是类似的,希望构建一些基本的逻辑单元阵列,用户可根据自身需求定义其功能。光芯片的基本单元是定向耦合器(directional coupler, 以下简称DC)。因而如何实现DC分光比的动态可调节,是需要解决的关键问题。典型的做法是以两个3dB的DC构成一个Mach-Zehnder干涉仪,在干涉仪的一条臂上通过热效应调节相位,进而达到分光比的动态调节,如下图所示。该方法需要额外的功率输出,当DC的数目增大时,功耗也相应增大。另外该方法中单个逻辑单元需要两个DC, 浪费了较多的芯片面积,增大了产品成本。

(图片来自ntt-review)

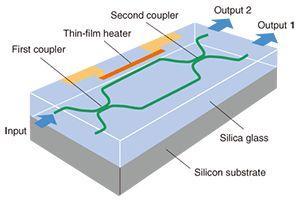

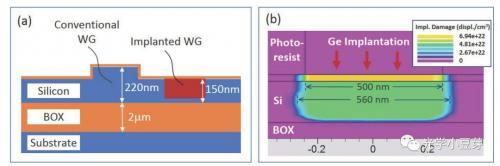

Reed研究组采用Ge离子注入的办法制备波导,该波导可通过激光退火的方法擦除。其制备艺与可擦除的光栅耦合器(硅光芯片的晶圆级测试)相似。Ge离子注入后,硅的晶格发生位移,引起波导有效折射率的改变。Ge离子注入后的波导,结构示意图如下图所示,Ge离子的注入深度约140nm。

(图片来自文献1)

借助于Ge离子注入波导,研究人员提出了两种分光比可调的定向耦合器结构,如下图所示。

(图片来自文献1)

左图是正常DC中的一根波导由注入波导代替,右图是在两根普通波导中间插入一根注入波导,借助其实现光场的耦合。红色区域为注入波导,其耦合区域的长度可以通过激光退火的方法进行改变,进而达到对分光比的调节,如下图所示。激光束在注入波导区域来回扫描,可逐步减小注入波导的长度,进而导致drop端口的能量减小。

(图片来自文献1)

以此DC为基础,研究人员进一步演示了1x4和2x2的光开光,如下图所示,

(图片来自文献1)

其中1x4的光开关由三个DC构成,2x2的光开光由四个DC构成。这些DC的分光比都是可调节的,通过改变分光比,光场可以从不同端口输出,对应不同的逻辑门操作。

研究人员进一步提出了一个较复杂的集成光路结构,通过DC分光比的改变,该光路可分别实现PSM4, WDM4和QAM的发送光路,如下图所示,

(图片来自文献1)

最初的光路如图a所示,改变MUX前端的DC分光比,使得光场不经过MUX,直接到输出端,对应为PSM4;光场经过MUX, 再传输到单个GC输出端,对应为WDM4; 选取两组MOD, 控制好它们间的相对相位为pi/2,就可以实现QAM编码。该光路设计非常巧妙,fab只需提供给用户类似图a的光芯片,然后用户再根据自身需求,自定义逻辑功能,也就是实现所谓的光学FPGA。由于出厂芯片里的光路一致,不需要额外定制,光芯片的成本也相应地降低。

总体说来,该进展的设计非常巧妙,借助于可擦除DC,实现了可编程的集成光路。这也许是未来集成光路的一个重点发展方向。但是目前来看,该方案的损耗还比较大,普通波导和注入波导的转换损耗接近1dB, 其传输损耗也大于一般硅波导的传输损耗。当多个DC组成逻辑阵列时,这么大的损耗显然会影响其进一步的应用与推广。当务之急是进一步改进工艺,实现较低的损耗,进而实现较复杂的逻辑阵列。

APP下载

APP下载 登录

登录

热门文章

热门文章