作者/Ted Marena 美高森美公司SoC/FPGA产品总监

以太网连接的日益普及和不断增加的降成本压力,是不可阻挡的两大网络趋势。由于网络和物联网(IoT)不断扩张,使得以太网端口的性能持续增加,并且应用于更广泛的各种产品。网络运营商面临两个巨大压力,首先是要大幅降低资本支出(CAPEX/OPEX),同时要提供更快性能以支持消费者应用,如4 K视频和无处不在的云连接。为了帮助架构师满足这些市场需求,我们需要重新定义中端密度FPGA特性:低成本、低功耗,并且可以满足通讯应用中以太网互联的性能要求。

这些新市场向设计以太网通信设备的供应商提出了重大的挑战。以太网的重大优势在于1 Gbps至10 Gbps线速率,而人们正在设计丰富的接入和网关设备,从而在网络边缘提供额外的计算能力。为了以更低成本提供这些解决方案,我们需要从整体系统的角度来考虑这个应用。为了降低成本,可以采用功耗更低的解决方案,从而取消风扇或散热片;或者不采用专用桥接产品,转而在SFP外形尺寸中实施这种功能,从而缩减PCB规格和总体外形尺寸。这些解决方案需要具备合适的以太网连接性、更低功耗,以及采用成本优化的小封装产品。现在,系统架构师拥有的解决方案能够帮助他们在更小外形尺寸中提供更节能的以太网接口,所有这些都需要成本优化、灵活的FPGA。

1低成本要求***商通信模块占用空间

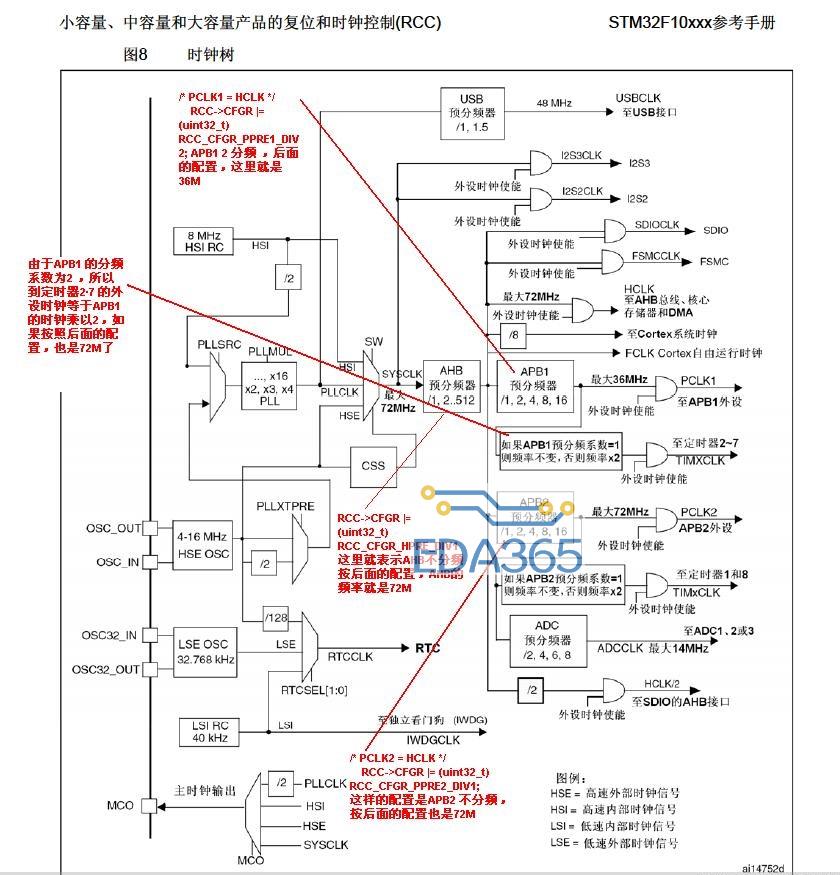

更低综合成本的需求正引领开发人员大幅减少通信产品占用的空间,而FPGA通常是以太网应用的关键设计部件。今天,市场上出现了一种优化的中密度FPGA产品,可以提供合适的接口性能,并保持了最低功耗和最小尺寸。许多现有的低密度FPGA拥有小封装,但接口性能不足(如不支持10 Gbps收发器),而大多数中密度FPGA的封装尺寸又偏大,且功耗颇高。而新的需求是更小物理封装中必须包含的关键特征包括10 Gbps收发器、大量嵌入式存储器、众多3.3 V I/O管脚,以及支持更新的存储器标准。具有这些能力、拥有功耗优化架构的中阶密度FPGA是即将到来的小型化解决方案的关键实现因素。

图1 小尺寸、低功耗、中阶密度且支持10 Gbps以太网的FPGA

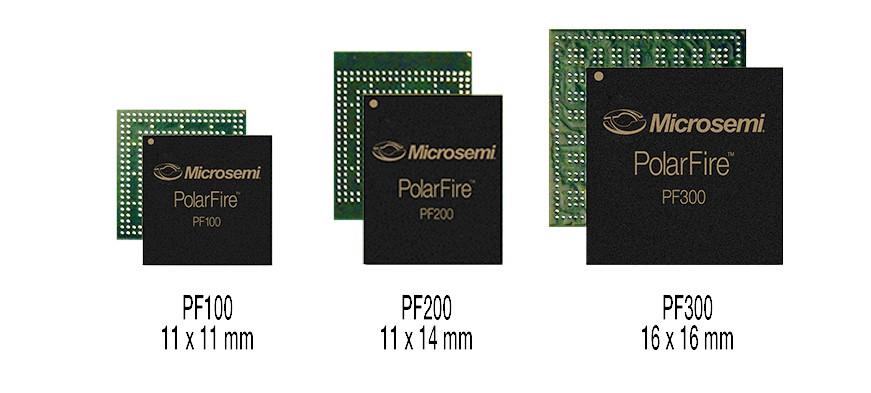

显然光模块或SFP类模块有明确的小尺寸要求。许多以太网通信产品都有SFP或类似的槽位以提供收发器接口,通常以1 Gbps至10 Gbps速率运行。能够在这些模块中实施各种功能的产品具有系统级的灵活性,并将提供更低成本的解决方案。例如,支持10 Gbps以太网的网关不一定需要同步网络定时,如SyncE或IEEE 1588。如果这类产品提供了SFP槽位,则可以使用特别设计并且支持SyncE的SFP来实现同步网络定时,此举使得整个网关产品设计时不再需要考虑SyncE功能,为不需要此功能的客户降低了总成本,而需要SyncE网络定时的用户,只需简单地插入支持SyncE功能的SFP模块。虽然许多小封装的低端FPGA可满足这种应用的尺寸要求,但是,低端FPGA无法提供必要的逻辑资源和性能。而典型的中阶FPGA支持10 Gbps以太网,但其高功耗和大尺寸却又不适用于SFP模块。PolarFire FPGA系列在仅11 mm宽的封装中可提供两种密度。这些器件针对成本和低功耗进行了优化,并且拥有高达10 Gbps以太网接口能力。

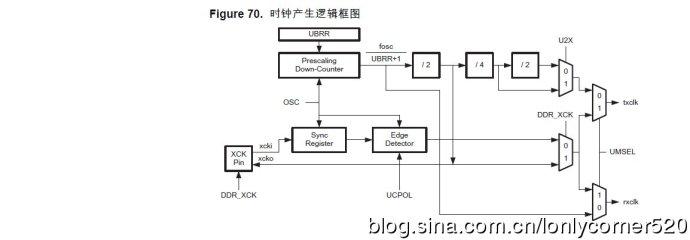

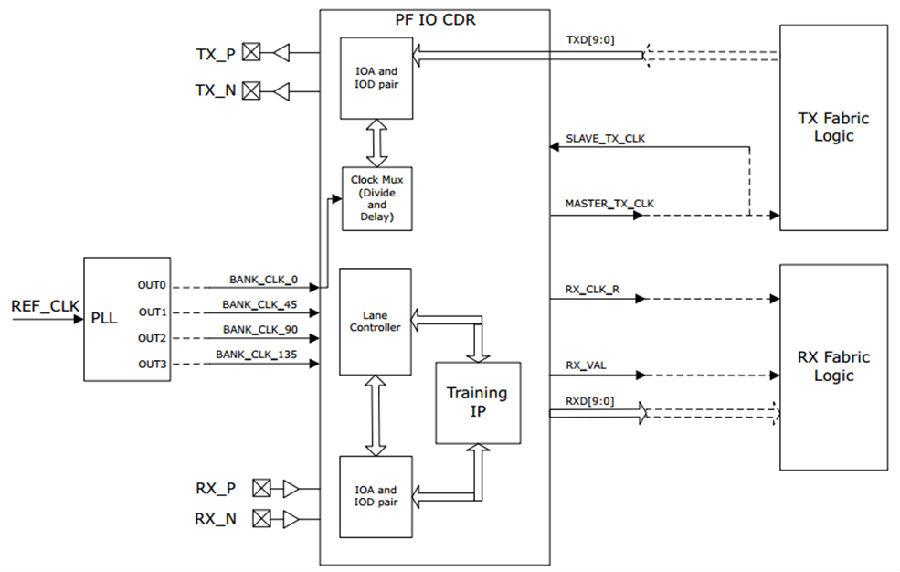

高效能千兆以太网接口正推动系统架构发生变化。许多通信产品开发商正在日益增多连接中采用的千兆位以太网。这些连接不再仅仅用于传输数据负载,而是普遍用于传输控制、管理、状态信号等。通常这些增长的千兆以太网接口将通过汇聚或复用成10 G以太网。传统的中阶FPGA可以支持这些1 Gbps至10 Gbps的速率,但需要串行收发器来实施1 G SGMII接口和10 G10 BASE-R或10 BASE-KR。而更理想的器件是可以用通用的I/O管脚来支持SGMII,如图2所示。

图2 在GPIO中实施SGMII的FPGA

传统中阶FPGA并不拥有这种特征,因此,必须使用串行收发器。除非使用非常昂贵的更高密度FPGA,否则这些串行收发器接口通常数量较少,而显得尤其宝贵。设计人员通常并不需要非常多的FPGA逻辑资源,但是,由于他们需要额外的串行收发器,因此被迫选择这类昂贵大器件。此外,这些大器件要求采用更大的封装尺寸。这些现有解决方案增加了功耗和成本,与OPEX需求相悖。

2新型PolarFire FPGA提供功耗优化的中阶密度

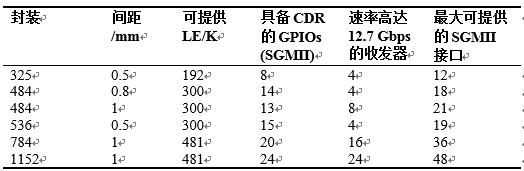

新型PolarFire FPGA提供功耗优化的中阶密度,应对众多GigE和10 GigE连接的要求。该系列从100 K LE至500 K LE,具有8至24个12.7 Gbps收发器,支持1 Gbps至10Gbps以太网。PolarFire FPGA与众不同的优点是在1.25 Gbps的高速LVDS I/O内集成了时钟和数据恢复(CDR)电路,使器件能够在一些特定的GPIO引脚上支持SGMII接口。现在,在千兆和万兆以太网混合应用中使用Polarfire,可以灵活地选择使用收发器或具有CDR的GPIO引脚来支持这些接口,如表1所示。

表1 GPIO中带有CDR的PolarFire FPGA系列

这样工程师就不必再为了增加串行收发器而选择封装更大的器件。PolarFire FPGA使他们可以选择更小的封装。这些GPIO CDR的功耗也比收发器低,降低了多个GigE连接应用的总功耗,有利于降低CAPEX/OPEX。

在通信应用中降低功耗的需求日益迫切。在功耗预算中,FPGA通常占了不小的比重。FPGA功耗的两个决定因素是静态功耗和串行收发器功耗。PolarFire FPGA在这两方面都非常出色。在SRAM FPGA中,静态功耗达总功耗的一半。这是因为这些器件已经使用很高级的生产工艺,晶体管尺寸的变小也使得静态功耗成为总功耗的主要组成。相反,PolarFire FPGA使用的是FLASH工艺,使得其静态功耗大约仅仅相当于SRAM器件的1/10。另外功耗占比较大的是串行收发器。对于中阶密度SRAM FPGA来说,通常每个10 Gbps接口功耗为160 mW至200 mW。PolarFire FPGA的同样功能通常仅消耗90 mW。此外,PolarFire还能够在GPIO中实现SGMII。当采用这种接口时,每个1 Gbps接口的功耗通常小于30 mW。由于静态功耗最低,且拥有最节能的1 Gbps和10 Gbps以太网接口,因此,与类似中阶密度SRAM FPGA相比,PolarFire FPGA的总功耗降低幅度高达50%。

3结论

以太网通信新需求推动工程师寻找新的解决方案。现在,中阶密度FPGA可以很好地应对1 Gbps 和10 Gbps以太网应用中。不管这些应用是接入网、SFP、网关、路由器或其它设备,设计人员都不再为了应对必需的要求而被迫牺牲成本和功率效率。PolarFire中端FPGA的低功耗、小尺寸,并拥有优化的以太网接口,这个特性能够满足以太网通信市场的新需求。

APP下载

APP下载 登录

登录

热门文章

热门文章