一直以来,设计人员为迅速发展的市场如消费电子和汽车等开发产品时,都面对严峻的上市时间压力。但是现在,这些严格的时间要求已经转移至其它许多领域,包括嵌入式控制和工业设计。

毋庸置疑,近年来谈论最多的芯片设计趋势是转向系统级芯片 (System-on-a-chip; SoC) -- 透过工艺技术和设计方法的突飞猛进而得以实现。但是SoC的发展进程仍然缓慢,并且对市场的变化非常敏感。此外,开发SoC本质上是一项成本高昂的高风险事业。极少公司拥有充足资源,能负担将SoC产品发展成为ASIC般生产所需的非经常性工程开支 (NRE),即使公司拥有足够资源也必须仔细考虑取得投资回报的机会。

在业内,迅速将产品推出市场的意愿非常重要。产品销售每推迟一周都会对营业额造成损失:举例说,如果产品的平均售价为1,500美元,而其制造商预计销量将推高至每周100件,那么,设计推迟三个月便会带来超过100万美元的损失。

因此,设计人员期望将现场可编程门阵列 (FPGA) 作为灵活的工业设计平台。这一趋势在工业无线通信设计方面更加明显,而本文稍后将加以叙述。在这种应用中,最初考虑的是采用专用标准产品 (ASSP),然后是专用集成电路(ASIC)。但是当考虑到上市时间、实施灵活性及未来废弃过时等问题时,设计小组决定转向FPGA来进行项目实施。

正如我们所料,上市时间压力并不是导致设计人员转向可编程逻辑器件在工业设计中获得增值功能的唯一推动力。当今的工艺几何学能够实现新一代的可编程逻辑器件,能以更高的速度提供更多更高速的逻辑,和更快的而且I/O更快、更低的价位更低。因此,FPGA现能用于嵌入式应用,而过去由于性能缘故,只有ASIC或ASSP才能达到这些要求。

现今的高功能FPGA不再局限于引进系统粘合逻辑,还可作为SoC平台,让工业设计人员轻易地修改以进行变更、修复缺陷,或在用户需要升级和配合市场发展时创制未来的衍生产品。那些先前选择半定制ASSP的设计人员,现已不需要再接受应用中未够理想的解决方案;而可以通过较使用ASIC更快的速度构建以定制FPGA为基础的方案,同时能适应变化多端的市场需求。

FPGA使用量增加的另一个原因是可编程到器件可编程加入的IP模块数量和范围大大增加,包括各种标准功能如广泛用于工业应用的8051微控制器。这类预校验和测试的IP模块专为可编程逻辑应用而优化,使设计人员能够快速构建系统并将其编程入FPGA。IP内核通常以网表或RTL资源形式提供,所以,设计人员无需更改便可快速使用,或者按照设计要求进行配置。

例如,Actel的Core8051与8051指令集相容,能让设计人员借助对现有微控制器架构方面的经验,发挥器件中具现有的大量代码和工具的优势,进一步缩短开发周期。通常,这类内核都具有额外特性:如Core8051拥有片上调试能力,能于简化内核在深度嵌入时简化的系统调试,协助设计人员更快地将产品推出市场。

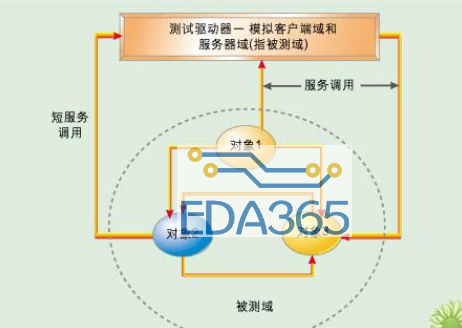

当年产量高达在10万件以内时,FPGA可以是一个出色的平台,能满足许多工业和嵌入式控制市场区间的需要。以微控制器为基础的SoC的发展有两个主要因素,分别是需要集成的元件或外设数量,以及所选元件的应用软件和专用驱动程序的集成。在理想情况下,设计人员当然希望以减少工艺步骤序和元件数来缩短开发时间。此外,他们也会简化应用软件的集成。在FPGA内使用FPGA内的可综合或“软”IP平台是简化设计过程和缩短上市时间的现代化解决方案。在流程图 (图1) 中,我们比较了使用大量IP内核构建微控制器SoC的关键步骤和使用IP平台开发FPGA设计所需的步骤。

l ),如图3所示,使设计人员能够观察Actel内核的工作情况,并迅速和有效地创建和模拟衍生产品设计。该套件可以大幅减少系统校验时间。它还包括一个可重编程ProASICPLUS FPGA、先前提到在器件上编程的网络服务器设计、网络服务器示范代码范例、所有相应的电缆、FS2 System Analyzer和 Keil µVision评估软件包,以及可供选择性的FlashPRO Lite编程器。

通过平台IP的方式,部署使用FPGA的优势显而易见,就像最近设计的模块化无线工业网络,用于高噪声杂讯工厂环境和制造自动化中。设计小组最初想用分立ASSP,但很快发现这方式并不能在获得正确的功能组合同时满足尺寸和功率需求。

换句话说,设计人员只可在ASIC和FPGA之间选择。项目成本分析研究显示,对于所预计的模块批量,ASIC和FPGA器件的成本接近;但是FPGA毋需任何NRE投资。因此,设计小组决定采用FPGA方案。

当设计小组考虑项目所需的IP时,更加认识到FPGA在成本和上市时间方面具有更大优势。 由于FPGA供应商已经拥有项目所需的大多数IP,因此设计小组只需开发少量特别的IP。使用预开发和校验IP能缩短设计周期长达六个月,让设计小组可以更快的速度和更短的时间将产品推向市场。而更短的上市时间可带来实在的财务成果。因为产品占据的市场份额大于预期,所以推动明显地增加了销售和利润的显着增加。

与此同时,设计小组可以根据较大型用户的应用和特定需求定制模块,并且在毋须替换整个线路板的情况下进行现场产品升级,其中只需要对FPGA进行重新编程。此举能降低用户的整体拥有成本、增加产品的认知价值,并扩大市场需求。

工业设计人员所面对的上市时间压力从未如此巨大。不论是设计网络接口、电机控制器、逻辑控制器、通信系统、或任何数以百计的工业应用,FPGA结合种类繁多的可用IP正成为工业设计的优选方案。就上市时间、执行的灵活性及未来的产品废弃过时等因素而言,FPGA较ASSP和ASIC解决方案具有更多优势。此外,因为许多工业应用从未达到大批量,FPGA常较传统的ASIC方案提供更多的成本节省。设计人员能够迅速编程把功能编程并在应用产品中测试产品,然后对功能规格的变化进行重新编程,自然对工业工程师别具吸引力。这些特性再结合目前在性能、尺寸和价格方面的进步,可让工业设计人员透过所熟悉的标准迅速将产品推向市场,并使产品留存在市场的留存时间和获得的销售收入提升至最高。

APP下载

APP下载 登录

登录

热门文章

热门文章