摘要:在飞行模拟器的设计中,为了使数据能够快速有效地在飞行模拟器的各个模块之间进行高速传递,提出了一种使用FPGA作为CAN总线节点结构中的核心处理器的设计方法,并完成了飞行模拟器通信接口的软硬件设计。采用Verilog HDL进行编程,能够完成对SJA1000总线控制器的有效读写。实际测试表明,相较于单片机作为处理器,本设计可扩展性好,易于修改和移植,能降低模拟器成本。

飞行模拟器是现代飞行员训练的必需设备,它是一种由计算机实时控制、多系统协调工作、能模拟真实飞行环境的模拟设备。相较于利用飞机的飞行训练而言,利用飞行模拟器的模拟飞行训练不仅不受天气等自然条件的制约,而且没有后勤、机务保障以及飞行安全等因素的限制。国内外许多单位均研制了各种不同种类和规模的训练模拟器,并取得良好的训练效果,保证了飞行任务的圆满完成。

在飞行模拟器的设计中,要求大量的信息能够快速有效地在飞行模拟器的各个模块之间进行高速传递,这就需要一定的通信接口协议来实现数据的交互。目前,飞行模拟器通常采用CAN总线作为通信协议,并采用单片机作为微处理器,可扩展性差。文章根据飞行模拟器的结构特点,分析了现场总线技术和FPGA技术的发展,根据飞行模拟器的实际需要和总线自身特点,选用了CAN总线来作为主机和现场设备的通信方式,并使用FPGA作为CAN总线节点结构中的核心处理器,对飞行模拟器通信接口进行了设计。

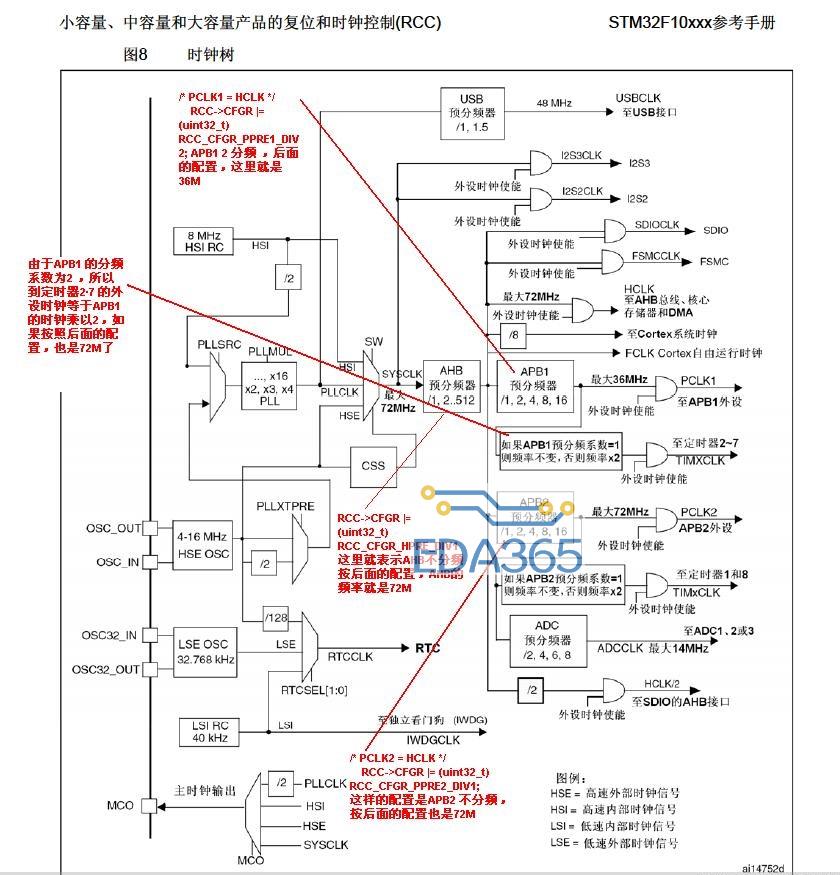

1 硬件系统设计

CAN(Controller Area Network)总线是一种串行通信总线,是国际上应用最广泛的开放式现场总线之一。CAN最早被设计作为汽车环境中微控制器的通讯,但由于其灵活性好、可靠性高、功能完善,已经被广泛应用到各个自动控制领域,CAN总线具有根据优先级的多主结构、可靠的错误检测和处理机制、传输速率高(最高可达1 Mb/s)、传输距离远(波特率低于5 kb/s时最远可达10 km),克服了RS-485网络的低总线利用率、单主从结构、无硬件错误检测的不足。在飞行模拟器的设计过程中,主控机需要与多个模块进行交互,选用 CAN总线接口是非常适合的。

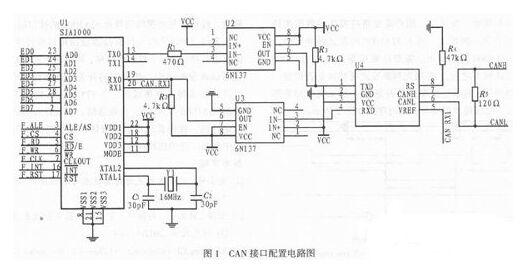

飞行模拟器通信接口的硬件设计,以CAN总线作为通信协议,选用ALTERA公司CYCLONE系列EP1C6Q240C8作为CAN节点的核心处理器,采用Philips公司的SJA1000T作为CAN总线控制器,在CAN总线控制器与CAN物理总线之间选用PCA82C250作为CAN收发器,为了增强抗干扰能力,

保护CAN总线控制器,在SJA1000T与PCA82C250之间使用6N137进行光电隔离,其速度为10 MHz。在Quartus II软件中运用Verilog对FPGA编程,实现对SJA1000T的控制及CAN节点之间的通信功能。接口电路设计如图1所示。

SJA1000芯片是一款独立的CAN总线控制器,相对于它的前一款PCA82C200,SJA1000是在原有的BasicCAN模式的基础上增加了PeliCAN模式,这种模式能够支持CAN2.0B协议。为了提高SJA1000的总线驱动能力,在SJA1000与CAN总线之间加入了 PCA82C250总线收发器,其主要功能是增大通信距离,提高系统的瞬间抗干扰能力,保护总线,降低射频干扰,实现热防护等。

系统设计中选用FPGA作为CAN总线节点的核心处理器,能够在速度和体积上有更好的适应性,可以增强飞行模拟器通信接口设计的灵活性和可扩展性,因为在飞行模拟器设计中,有时还需要用到其他通信接口,比如括RS232和RS422。EP1C6Q240是ALTERA公司推出的一款高性价比的 FPGA,工作电压为3.3 V,内核电压1.5 V,采用0.13μm工艺技术,其内部具有5 980个LEs,含有20个MK4 RAM块(128×36 bits),总的RAM空间共计92 160比特,内嵌2个锁相环电路,最大用户I/O为185个,配置芯片选用EPCS1,对于FPGA的下载方式,通常可以采用JTAG方式和AS方式,不同下载方式,其硬件连接方式不用。JTAG方式,下载程序到FPGA芯片内RAM中,FPGA芯片内的程序掉电后无法保存,JTAG下载方式适合调试程序时使用,而AS方式则能将程序下载到配置芯片内,配置芯片内的程序掉电后也可以保存,再次上电后自动装载到FPGA内并由FPGA开始运行。

在CAN总线接口硬件设计中,主要是CAN总线控制器与FPGA以及CAN总线控制器与CAN总线收发器之间的接口电路设计。在设计时,相比于采用单片机作为微处理器的设计,FPGA具有丰富的I/O端口,为了使FPGA的3.3V I/O接口电平与SJA1000的5 V TTL电平标准相匹配,在FPGA与SJA1000连接时需要使用74ALVC164245电平转换器,这样CAN总线控制器SJA1000的 AD0~AD7、片选信号CS、RD、WR、ALE、INT、MODE分别经过电平转换器再与FPGA的I/O相连。为了增强抗干扰能力,总线控制器 SJA1000的发送输出端TX0与接收输入端RX0分别经集成光电耦合器6N137,与总线收发器PCA82C250的TXD和RXD相连,PCA82C250的CANH、CANL端口直接与CAN物理总线相连。PCA82C250是 CAN总线控制器和物理总线之间的接口,具有可向总线差动发送数据和从CAN总线控制器差动接收数据的功能。另外,SJA1000的RX1引脚与 PCA82C250的VREF引脚相连,使用输入比较器旁路功能,可减少内部延时,增加正常通信的总线长度。

2 软件系统设计

CAN总线节点的软件的设计主要是对FPGA进行编程,一方面对飞行模拟器各类接口数据的采集和输出,另一方面是对SJA1000的接口逻辑程序,来控制CAN总线的工作方式和工作状态,进行数据的发送和接收。这里主要介绍FPGA对总线控制器的程序设计,主要包括对SJA1000的初始化逻辑、数据发送逻辑和数据接收逻辑。由于SJA1000地址总线与数据总线复用,这就需要FPGA不仅要产生SJA1000读写控制引脚的信号逻辑,还需要产生对 SJA1000的寻址信号,实际上是一个向SJA1000写地址的过程。因此设计的关键就是把SJA1000中的寄存器地址当成数据写入到SJA1000 中,同时配合地址锁存信号ALE和写允许信号WR完成对SJA1000特定寄存器的命令字写入。

2.1 SJA1000初始化逻辑

初始化逻辑的主要功能是在系统上电或重启后,对SJA1000进行初始化,以确定工作主频、波特率、输出特性等。SJA1000支持两种模式,即 BasicCAN模式和PeliCAN模式,BasicCAN模式是上电后默认的操作模式。SJA1000的初始化逻辑主要包括工作方式的设置、验收滤波方式的设置、验收屏蔽寄存器(AMR)和验收代码寄存器(ACH)的设置、中断允许寄存器(IER)的设置、总线定时寄存器(BTR0、BTR1)、输出控制寄存器(OCR)和时钟分频器(CDR)的设置等。在完成SJA1000的初始化设置以后,SJA1000就可以回到工作状态,进行正常的通信任务。

APP下载

APP下载 登录

登录

热门文章

热门文章