有些朋友自已想制板,我看了一些书,自己也画过板,总结一下。希望对那些跃跃欲试的朋友有所帮助。首先是原理图的问题,最小系统板(包括CAN,好像就是传说中清华的那块板),芯片的外围滤波和电源的滤波都是经典的。不过,都是按8M的设计的,目前很多的系统板都是如此。HCS的管脚很多,如何配置利用好,是留下接口还是直接拿来用要量力而行,一般的,SCI肯定要的,LED作指示,SPI,CAN都可以搞上,一个芯片可以做。PS:上次有个朋友留言说HCS12DG只能用串联晶振方式,是不对的。串联并联都可以,而且一般用无源晶振,便宜。

接着谈一下PCB。PCB这个最好按飞思卡尔的DS上的布线布置晶振,PLL的外围电容,因为这两个都直接地影响到系统的稳定性。

特别注意:

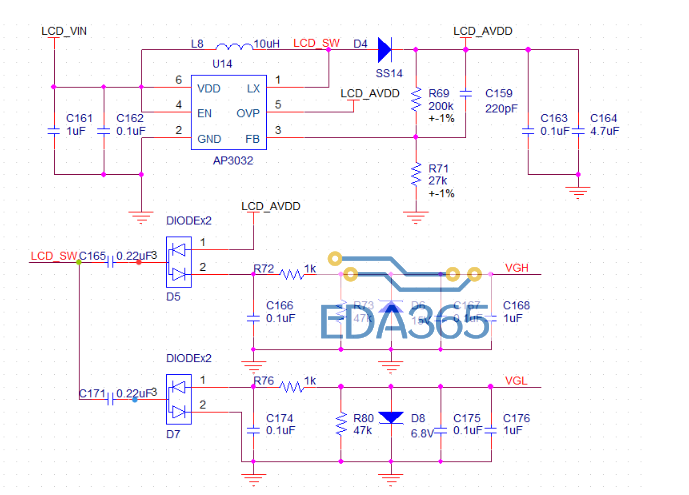

1、电源要处理干净。

CU可能产生短暂的能量消耗峰值,类似于一个脉冲,而脉冲有一个显著高频的傅氏光谱分量,容易产生电磁干扰问题。通常应该应用一个0.1uF的电容滤波,而一个0.01uF的电容应该放在每个电路的电源和接地之间,这个电容应该尽可能靠近每个IC管脚。除了这些电容,一个10--470uF的电容也应该放在电源稳压前面做储能。最后,电源和MCU中间添加一个磁珠除干扰。

2、时钟晶振的处理。

布线时晶振下面最好不好走线。一般用16MHz的晶体来产生8MHZ的基准时钟。频率越高谐波会越显著,晶振要离MCU近,而且外壳需要接地。在高频很敏感的场合,无用的输入管脚需要作一些处理,如下拉,上拉等等,还好,飞思的单片机有51K左右的上拉。

3、接地处理。

地被认为是0V,若电动势失真,那么会出问题的。因此,必须确保所有的电路引脚都共用一个参考地,并且这个参考地是非常稳定的。多个连接点接地可以避免“ 地”的微弱失真,即多点接地。最高级的做法是“混合接地”即单点接地和多点接地配合使用。它对各单独的数字、模拟、输入输出以及PCB元件都非常重要。比如:SCI LED VSS等每个小系统都共用一个单独的接地点,而在各个小系统里采用多点接地。这对提高系统的稳定性有效,特别是高频时。

热门文章

更多

热门文章

更多