1.4.1中断信号与中断控制器的连接关系

不同的处理器使用的中断控制器不同,如x86处理器使用APIC(Advanced Programmable Interrupt Controller)中断控制器,而PowerPC处理器使用MPIC(Multiprocessor Interrupt Controller)中断控制器。这些中断控制器都提供了一些外部中断请求引脚IRQ_PINx#。外部设备,包括PCI设备可以使用这些引脚向处理器提交中断请求。

但是PCI总线规范没有规定PCI设备的INTx信号如何与中断控制器的IRQ_PINx#信号相连,这为系统软件的设计带来了一定的困难,为此系统软件使用中断路由表存放PCI设备的INTx信号与中断控制器的连接关系。在x86处理器系统中,BIOS可以提供这个中断路由表,而在PowerPC处理器中Firmware也可以提供这个中断路由表。

在一些简单的嵌入式处理器系统中,Firmware并没有提供中断路由表,此时系统软件开发者需要事先了解PCI设备的INTx信号与中断控制器的连接关系。此时外部设备与中断控制器的连接关系由硬件设计人员指定。

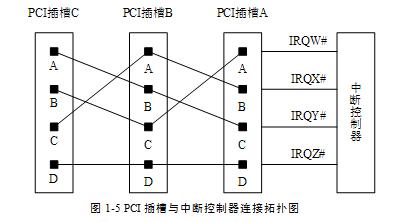

我们假设在一个处理器系统中,共有3个PCI插槽(分别为PCI插槽A、B和C),这些PCI插槽与中断控制器的IRQ_PINx引脚(分别为IRQW#、IRQX#、IRQY#和IRQZ#)可以按照图1‑5所示的拓扑结构进行连接。

在一个处理器系统中,多数PCI设备仅使用INTA#信号,很少使用INTB#和INTC#信号,而INTD#信号更是极少使用。在PCI总线中,PCI设备配置空间的Interrupt Pin寄存器记录该设备究竟使用哪个INTx信号,该寄存器的详细介绍见第2.3.2节。

1.4.2中断信号与PCI总线的连接关系

在PCI总线中,INTx信号属于边带信号。所谓边带信号是指这些信号在PCI总线中是可选信号,而且只能在一个处理器系统的内部使用,并不能离开这个处理器环境。PCI桥也不会处理这些边带信号。这给PCI设备将中断请求发向处理器带来了一些困难,特别是给挂接在PCI桥之下的PCI设备进行中断请求带来了一些麻烦。

在一些嵌入式处理器系统中,这个问题较易解决。因为嵌入式处理器系统很清楚在当前系统中存在多少个PCI设备,这些PCI设备使用了哪些中断资源。在多数嵌入式处理器系统中,PCI设备的数量小于中断控制器提供的外部中断请求引脚数,而且在嵌入式系统中,多数PCI设备仅使用INTA#信号提交中断请求。

在这类处理器系统中,可能并不含有PCI桥,因而PCI设备的中断请求信号与中断控制器的连接关系较易确定。而在这类处理器系统中,即便存在PCI桥,来自PCI桥之下的PCI设备的中断请求也较易处理。

在多数情况下,嵌入式处理器系统使用的PCI设备仅使用INTA#信号进行中断请求,所以只要将这些INTA#信号挂接到中断控制器的独立IRQ_PIN#引脚上即可。这样每一个PCI设备都可以独占一个单独的中断引脚。

而在x86处理器系统中,这个问题需要BIOS参与来解决。在x86处理器系统中,有许多PCI插槽,处理器系统并不知道在这些插槽上将要挂接哪些PCI设备,而且也并不知道这些PCI设备到底需不需要使用所有的INTx#信号线。因此x86处理器系统必须要对各种情况进行处理。

x86处理器系统还经常使用PCI桥进行PCI总线扩展,扩展出来的PCI总线还可能挂接一些PCI插槽,这些插槽上INTx#信号仍然需要处理。PCI桥规范并没有要求桥片传递其下PCI设备的中断请求。事实上多数PCI桥也没有为下游PCI总线提供中断引脚INTx#,管理其下游总线的PCI设备。但是PCI桥规范推荐使用表1‑3建立下游PCI设备的INTx信号与上游PCI总线INTx信号之间的映射关系。

表1‑3PCI设备INTx#信号与PCI总线INTx#信号的映射关系

设备号 | PCI设备的INTx#信号 | PCI总线的INTx#信号 |

0, 4, 8, 12, 16, 20, 24, 28 | INTA# | INTA# |

INTB# | INTB# | |

INTC# | INTC# | |

INTD# | INTD# | |

1, 5, 9, 13, 17, 21, 25, 29 | INTA# | INTB# |

INTB# | INTC# | |

INTC# | INTD# | |

INTD# | INTA# | |

2, 6, 10, 14, 18, 22, 26, 30 | INTA# | INTC# |

INTB# | INTD# | |

INTC# | INTA# | |

INTD# | INTB# | |

3, 7, 11, 15, 19, 23, 27, 31 | INTA# | INTD# |

INTB# | INTA# | |

INTC# | INTB# | |

INTD# | INTC# |

我们举例说明该表的含义。在PCI桥下游总线上的PCI设备,如果其设备号为0,那么这个设备的INTA#引脚将和PCI总线的INTA#引脚相连;如果其设备号为1,其INTA#引脚将和PCI总线的INTB#引脚相连;如果其设备号为2,其INTA#引脚将和PCI总线的INTC#引脚相连;如果其设备号为3,其INTA#引脚将和PCI总线的INTD#引脚相连。

APP下载

APP下载 登录

登录

热门文章

热门文章