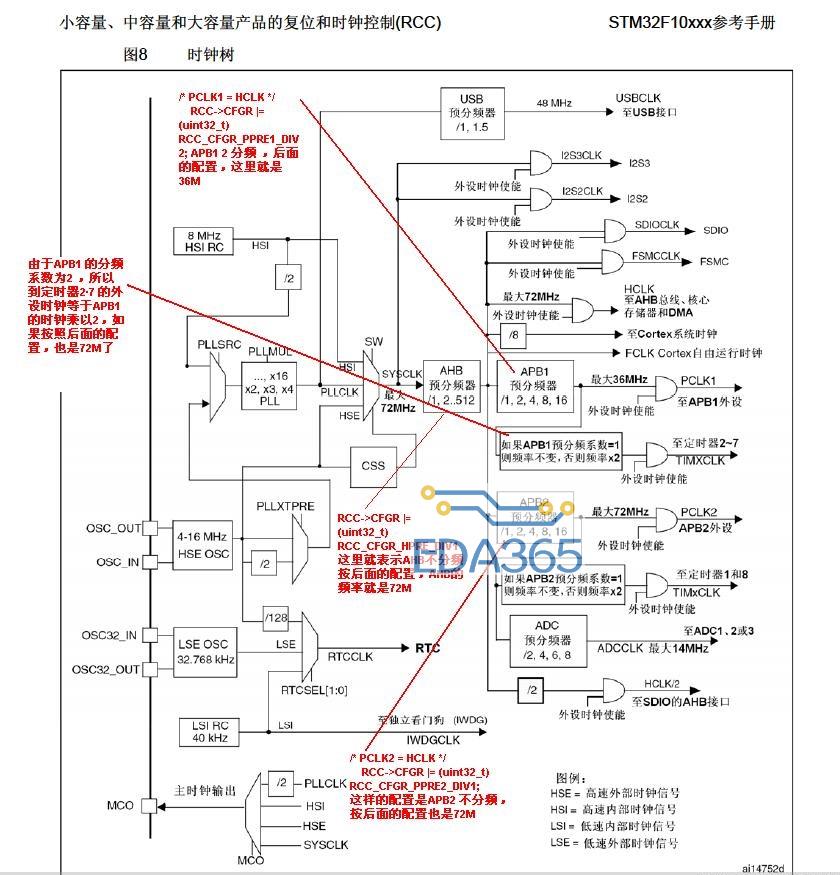

三种不同的时钟源可被用来驱动系统时钟(SYSCLK):

● HSI振荡器时钟

● HSE振荡器时钟

● PLL时钟 这些设备有以下2种二级时钟源:

● 40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC。RTC用于从停机/待机模式下自动唤醒系统。

● 32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK)。 当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

1.当HSI被用于作为PLL时钟的输入时,系统时钟能得到的最大频率是64MHz。

2.对于内部和外部时钟源的特性,请参考相应产品数据手册中“电气特性”章节。 用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。AHB和APB2域的最大频率是72MHz。APB1域的最大允许频率是36MHz。SDIO接口的时钟频率固定为HCLK/2。

RCC通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟。ADC时钟由高速APB2时钟经2、4、6或8分频后获得。

定时器时钟频率分配由硬件按以下2种情况自动设置: 1. 如果相应的APB预分频系数是1,定时器的时钟频率与所在APB总线频率一致。 2. 否则,定时器的时钟频率被设为与其相连的APB总线频率的2倍。

void RCC_Configuration(void)

{

SystemInit();

RCC_APB2PeriphClockCmd(USARTy_GPIO_CLK | USARTz_GPIO_CLK | RCC_APB2Periph_AFIO, ENABLE);

#ifndef USE_STM3210C_EVAL

RCC_APB2PeriphClockCmd(USARTy_CLK, ENABLE);

#else

RCC_APB1PeriphClockCmd(USARTy_CLK, ENABLE);

#endif

RCC_APB1PeriphClockCmd(USARTz_CLK, ENABLE);

}

APP下载

APP下载 登录

登录

热门文章

热门文章