1 引言

ARINC429 总线是广泛应用在航空电子系统中的一种通讯总线。PCMCIA/JEIDA接口是一种广泛应用在数码电子产品和便携式计算机上的PC 卡接口规范。在航空通信系统中使用便携式计算机进行通信调试,应用FPGA 来实现PCMCIA 规范接口并完成通信,使板卡具有体积小、性能高、可靠性好的特点。板卡在航空领域应用,方便了现场调试。

2 设计思路

2. 1 通信卡总体结构设计

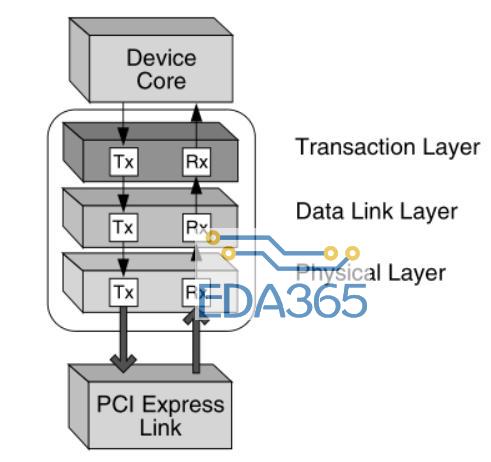

通信板卡功能的实现核心是FPGA 内部电路的设计,图1 就是FPGA 内部设计图梗概。设计采用PCMACIA 接口的16 根数据线与16 根地址线,可用存储空间达64KB,但使用的只是其中一小部分。

PCMCIA 规范规定16 位PC 卡有两种模式,MEMORYONLY 模式和I /O AND memory 模式,MEMORYONLY 模式只适用于纯粹做存储卡的PC 卡设备。设计采用I /O AND MEMORY 模式,但采用的只是MEMORY 操作,这相当于在MEMORY 空间里实现了一个设备,这个设备用来完成PCMCIA 主机和ARINC429 芯片的通信。

FPGA 内部要实现与HOST 主机连接的PCMCIA接口逻辑。PCMCIA 规范将卡的存储空间分为ATTRIBUTE MEMORY 和COMMON MEMORY 两部分,ATTRIBUTE MEMORY 主要用来实现卡的配置,在这里边实现了卡信息结构,以及配置寄存器,而在COMMON MEMORY 实现了用于与DEI1016 通信的设备。

在 FPGA 内部实现逻辑时,PCMCIA 接口部分相当于主设备,而内部的寄存器、ARINC429 设备都是从设备,在FPGA 内部必须实现对寄存器读写,对ARINC429 通信控制信号的时序,对ARINC429 接口的读写时序的实现是个重点。为了实现从DEI1016芯片接收数据,在FPGA 内部实现了一个64* 16bit的FIFO,待FIFO 半满时向PCMCIA 主机发出中断信号,主机从FIFO 中读走数据。由于从接受ARINC429 接口接收数据的时序比较复杂,采用状态机来实现。向DEI1016 发送数据时,由于DEI1016 内部有一个8* 32bit 的FIFO,PCMCIA 的数据线和ARINC429 的数据线都是16 位的,可以直接发送,一些控制信号可以通过寄存器操作或MEMORY 地址操作实现。

图1 通信卡总体结构框图

2. 2 PCMCIA 接口设计

2. 2. 1 PCMCIA/JEIDA 规范

PCMCIA/JEIDA 是由个人电脑存储卡国际组织和日本电气工业协会提出并推广的一个便携式卡接口规范。其特性如下:

( 1) 16 /32 位数据线

( 2) 20MB /S( 132MB /S) 速率,宽度周期100NS

( 3) 支持8 位/16 位DMA 操作

( 4) 兼容PCMCIA2. 1 /JEIDA4. 2 以及更早的版本,兼容32 位卡插槽

( 5) 硬件探测卡电压需求可以是5V,3. 3V,或更低

( 6) 支持多功能卡

( 7) 利用卡信息结构的扩展能力,可以确定卡功能和数据格式

2. 2. 2 卡信息结构和配置寄存器的设计

卡信息结构,简称CIS,是在卡的ATTRIBUTEMEMORY 空间里实现对卡进行配置的结构,相当于一个ROM 结构,主机通过读它来对卡进行配置,它必须从ATTRIBUTE MEMEORY 空间的00H 地址开始。它由很多的TUPLE 组成,每个TUPLE 有一定的结构,由若干字节组成,这些字节信息只存在于偶数字节地址空间,每个TUPLE 都固定的含有一个TUPLE 特有的序号和相对于下一个TUPLE 的偏移量,以及TUPLE 体,表明了一定的配置信息,或者功能说明。这些TUPLE 连成链,用结束TUPLE( 序号FFH) 表明链的结束。16 位PC 卡的TUPLE 最多257 个字节: 一个字节的TUPLE 号+ 一个字节的TUPLE 链域+ FFH 的TUPLE 体。一个链最多有256 个TUPLE。

必须要实现的TUPLE 有:

CISTPL - DEVICE: 5V 设备信息TUPLE,包含卡设备的信息。因为用的都是存储器操作,实现接口功能,设备速度是200NS,设备大小是两个512 字节的块,共1M 空间。序号是17H; CISTPL - CONFIG:

给出了ATTRIBUTE MEMORY 空间里配置寄存器的基地址0200H,给出了最后一个ENTRY TUPLE的序号是01H,以及配置寄存器的个数是1,就是配置选项寄存器,序号是1AH; CISTPL - CFTABLE -ENTRY: 配置入口TUPLE 明确了每一个需要的功能,不同的功能被不同的ENTRY TUPLE 区分,它被自己的配置入口序号所标记。在设计中选择I /OAND MEMORY 接口,使用的是MEMORY 映射I /O方式实现; 中断方式是脉冲中断; 使用的commonmemory 空间从0300H 开始,1K 大小,TUPLE 序号是1BH; CISTPL - VERS - 1: 这是卡制造商信息TUPLE,用PCMCIA2. 1 /JEIDA4. 2 版本,序号是15H; CISTPL - END: 链结束TUPLE,序号是FFH。

在卡的ATTRIBUTE MEMORY 空间里可有一个配置寄存器组,这些配置寄存器都是可读可写的,为了简化设计,一些可选寄存器都没有实现,只实现了必备的配置选项寄存器COR。这个配置选项寄存器的地址是在CIS 结构中给出的,在0200H 地址单元。一个8 位的寄存器。结构如下:

表1 配置选项寄存器

由主机写入该寄存器的内容,实现第7 位写1,卡被复位,第6 位写1 是电平中断模式,0是脉冲中断模式,后6 位写入CIS 结构中entry tuple 的序号,实现该入口对应的配置功能。只实现了一个entrytuple,是设置了一个common memory 设备( 也是存储空间) : 基地址0300 的1KB 空间。

在接口模块的MEMORY 读写操作中,配置空间的CIS 是只读的,COR 是可读可写的。16 位PC卡的读写操作属于异步时序,没有同步时钟。

2. 3 ARINC429 通信设计

2. 3. 1 DEI1016 接收数据时控制信号的实现

采用DEI1016和BD429来实现ARINC429数据的收发。HOST 向DEI1016 发送数据时,由于内部自带FIFO,可直接发送,但要区分发送的是WORD1 还是WORD2,还是控制寄存器数据。

HOST 从DEI1016 接收数据时,用有限状态机来实现读取控制信号时序,这一过程完成一个32 位字的接收,即一次DR1 或DR2 有效,两次OE1 或OE2 为低,两次16 位字的接收,实现过程如图2。其中OE1# /OE2#: 读出接收通道的数据; DR1# /DR2#: 该通道接收到了数据; SEL: 字选择信号。

图2 读取控制信号状态机

2. 3. 2 FPGA 内部接收FIFO 设计

当从DEI1016 接收数据时,在FPGA 内部实现了一个64* 16bit 的FIFO,该FIFO 从DEI1016 接收数据并缓存,PCMCIA 接口接收数据时只与FIFO进行通信。

当FIFO 从DEI1016 接收数据时,将FIFO 的写时钟信号和ARINC429 接口的通道1 或2 的读信号连接在一起,用ARINC429 的读信号做FIFO 的写时钟,而将FIFO 的写允许信号始终置为有效‘1’,当oe1 /oe2 的上升沿来临时,就对FIFO 进行写操作。

当PCMCIA 接口从FIFO 接收数据时,因为主机读信号是低有效的,所以用PCMCIA 接口的读信号下降沿做FIFO 的读时钟信号,而将读允许信号始终置为允许‘1’。

给FIFO 的发送端口固定的地址是0300H,主机从FIFO 中接收数据相当于对0300H 地址进行读操作。另外用FIFO 的半满信号做中断信号,即当FIFO 中存在32 个字时。FIFO 的接收数据线与DEI1016 的16 根数据线相连,发送数据线与PCMCIA接口的16 位数据线相连。

2. 3. 3 寄存器设计

为了便于对一些信号的控制以及上层软件访问的便利,在PCMCIA 规范规定的common memory 空间里实现了一个状态寄存器( SR) 和一个控制寄存器( CR) ,将一些控制和状态信号装入寄存器中固定的某位,以便上层软件的控制访问。

在common memory 的0308H 地址单元实现了一个状态寄存器,它是只读寄存器。第0 位是TXR信号量,为1 表示DEI1016 内部的FIFO 是空的,可以装入数据; 第1 位是FPGA 内部FIFO 空信号,为高表示空; 第3 位是FPGA 内部FIFO 满信号,为低表示满。

在common memory 的0310H 地址单元实现了一个控制寄存器,它是可读可写寄存器。第0 位是ENTX 信号,是DEI1016 发送数据允许信号,为1 表示允许发送; 第1 位是DEI1016 复位信号MR,低有效。

上层软件在控制向DEI1016 的发送缓冲区( FIFO) 写数据时,应先读出SR 的TXR 位,FIFO 为空时即TXR 为1 时才能让主机向FIFO 中写入数据。而用CR 的ENTX 位控制DEI1016 是否能发送数据时也应该先判断TXR,TXR 为高时,即发送FIFO 为空时,DEI1016 是不能发送数据的,只有为低时才能发送; 当TXR 为低时,也不能强行拉低ENTX,即发送FIFO 中有数据时,不能强行禁止发送,因为这样破坏了原有数据的完整性。

同样可以通过common memory 中的FIFO -EMPTY 信号控制主机从接收FIFO 中取数据; 还可以写DEI1016 的复位信号。

2. 4 存储空间设计概括

卡刚插入笔记本卡插槽的时候,主机主动读CIS 内容,然后可以写COR,进行配置。对DEI1016操作之前,要先写控制寄存器里的MR 信号,使DEI1016 复位后,再写入DEI1016 的控制寄存器,然后才可以进行数据的收发操作。接收数据就是响应中断信号( FIFO 的半满信号) ,从FIFO 中读取数据,直到判断出FIFO - EMPRY 信号有效。发送数据时,要先判断SR 里边的TXR 信号,当DEI1016 里的FIFO 为空时,再向FIFO 里发送数据,发送总字数不定,但不能超过DEI1016 内部FIFO 的容量8*32bit,发送之前拉低ENTX,且每次是先发送字一,再发送字二,字一,字二必须成对发送,发送完后拉高ENTX,允许DEI1016 发送数据。

在FPGA 内部实现可利用的存储区域概括起来如下:

表2 存储区域使用表

3 结束语

介绍了应用FPGA 完成PCMCIA 接口的ARINC429 通信卡的设计方案和其中的难点,通过本次设计也为其它应用FPGA 完成PCMCIA 接口的PC卡的设计提供了可借鉴方案。除了上述之外,上层应用程序和板卡的配合也是值得注意的

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多