随着USB2.0/DSP数字信号处理理论和计算机的不断发展,现代工业生产和科学技术研究都需要借助于数字处理方法。进行数字处理的先决条件是将所研究的对象进行数字化,因此数据采集与处理技术日益得到USB2.0/DSP重视。

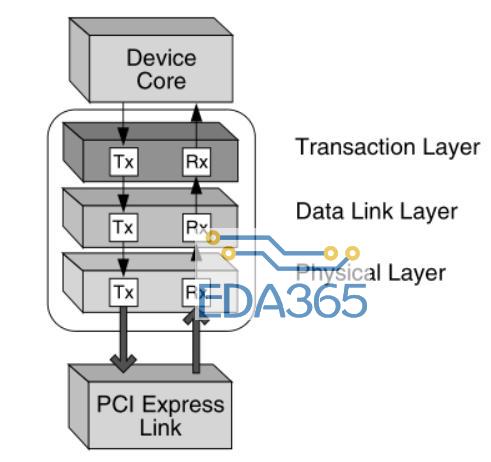

在图像USB2.0/DSP处理、瞬态信号检测、软件无线电等一些领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。现在的高速数据采集处理卡一般采用高性能数字信号处理器(DSP)和高速总线技术的框架结构。DSP用于完成计算量巨大的实时处理算法,高速总线技术则完成处理结果或者采样数据的快速传输。DSP主要采用TI或者ADI公司的产品,高速总线可以采用ISA、PCI、USB等总线技术。

目前,使用USB2.0/DSP比较广泛的是PCI总线,虽然其有很多优点,但是存在如下严重缺陷;易受机箱内环境的影响,受计算机插槽数量的地址、中断资源的限制而不可能挂接很多设备等。USB总线由于具有安装方便、高带这、易扩展等优点,其中USB2.0标准有着高达4800bps的传输速率,已经逐渐成为计算机接口的主流。

本文介绍一个采用USB2.0接口和高性能DSP的高速数据采集处理系统,主要是为光纤通信中密集波分复用系统的波长检测与调整所设计的,也可以应用于像图像处理、雷达信号处理等相关领域。

(2)ADS5422

ADS5422是由美国TI公司生产的高速并行14位模数转换器,其最高USB2.0/DSP采样频率达到62MHz,采样频率为100MHz时,SNR为72dB,SFDR为85dB。模拟信号输入可以是单端输入方式或者差分输入方式,最高输入信号峰峰值为4V,单一5V电源供电。输出数字信号完全兼容3.3V器件,并且提供输入信号满量程标志以及输出数字信号有效标志,从而方便和其它器件的连接。

(3)IDT72V2113

IDT72V2113是由美国IDT公司生产的高速大容量先进先出存储器件(FIFO)。其最高工作频率为133MHz;容量为512KB,可以通过引脚方便地将容量设置成512K×9bit或者256K×18bit两种方式;IDT72V2113可以设置标准工作模式或者FWFT(First Word FallThrough)工作模式,并提供全满、半满、全空、将满以及将空等五种标志信号;非常方便进行容量扩展。容量扩展是IDT72V2113的一大USB2.0/DSP特点,扩展方式可分为字长扩展和字深扩展。通过容易扩展可以由多片IDT72V2113形式更大容量的缓冲,并且电路连接简单、可靠。

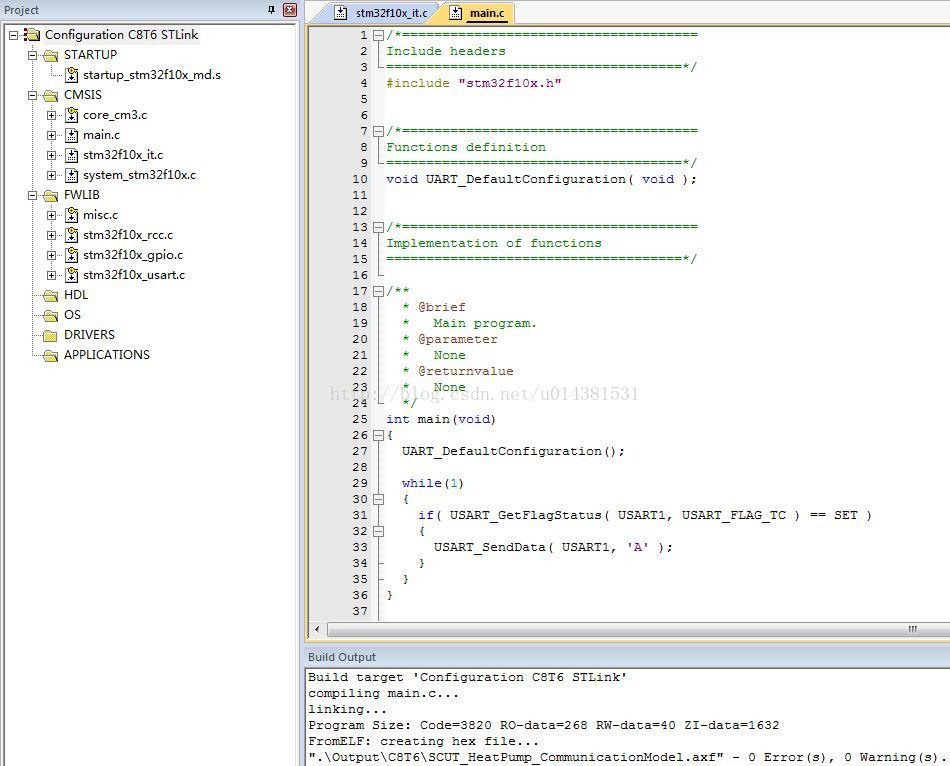

(4)CY7C68013

CY7C68013是美国Cypress公司推出的USB2.0芯片,是一个全面集成的解决方案,它占用更少的电路板空间,并缩短开发时间。CY7C68013主要结构如下:包括1个8051处理器、1个智能串行接口引擎(SIE)、1个USB收发器、16KB片上RAM(其中包括4KBFIFO)存储器以主1个通用可编程接口(GPIF)。

2.2 ADS5422与IDT72V2113的连接

虽然ADS5422的供电电压为5V,但其输出的数字信号电平USB2.0/DSP兼容3.3V电平,因此不需要电平转换芯片,只要将ADS5422的数据线与IDT72V2113的数据线相连即可。但是,ADS5422采样和存储采样数据到IDT72V3113中,这两个操作对时序配置要求非常严格,如果两者时序关系配合得不是很好,就会发生数据存储出错或者掉数。如何简单、可靠地实现采样和存储是设计这部分电路的难点。

一般的方法是,通过可编程逻辑器件(CPLD或FPGA)来实现ADC与FIFO存储器之间的时序,即由CPLD或FPGA来控制ADC采样和FIFO存储器的写操作。但是,通过仔细查看ADS5422和IDT72V2113的工作时序图,找到了一种简单可靠的实现方法,此方法不需要CPLD或FPGA就可以实现两者的时序配合。

首先分析ADS5422的工作时序图,如图3所示,其中t1为采样时钟上跳沿到输出数据无效之间的时间间隔,即数据保持时间,其大小为3ns。查看IDT72V2113的相关文档可知,对其进行写操作时,数据线的保持时间大于1ns即可满足要求。因此,ADS5422与IDT72V2113之间USB2.0/DSP的时序配合可以采用以下简单的实现方法:ADS5422的采样时钟和IDT72V2113的写时钟采用同一个时钟源,这样,每一个时钟的上跳沿,ADS5422进行模数转换,同时将上个时钟周期内输出的采样数据存储到DT72V2113内部。

2.3 C6203B与IDT72V2113的连接

C6203B与IDT72V2113的连接是通过C6203B外部扩展总线(XB)。C6203B的外部扩展总线(XB)宽度为32位,可以实现与同步FIFO无缝连接,可以同时无缝实现四个FIFO写接口或者实现3个FIFO写接口及1个FIFO读接口。通过无缝连接实现FIFO读接口,FIFO必须连接到XCE3上,数据USB2.0/DSP通过DMA方式从IDT72V2113传送到C6203B的片内RAM中,具体连接如图4所示。

图4中,4片IDT72V2113经过字长和字深扩展形成2MB的数据输入缓冲,输入数据总线(D0~D15)、输出数据总线(Q0~Q15)、读使能(REN)、读时钟(RCLK)、写使能(WEN)、写时钟(WCLK)和将空标志信号(PAE)是由4片IDT72V2113的相应信号组合形成的;XCE3为外部扩展总线(XB)的空间选择信号,XFCLK为外部扩展总线(XB)的输出时钟,EXT_INT4是C6203B的外部中断信号4,DX0用作通用输出口,控制IDT72V2113的写使能信号。

2.4 CY7C68013与C6203B的连接

CY7C68013是一个非常方便的USB2.0实现方案,它提供与DSP或者MCU连接的接口,连接方法有两种:SlaveFIFOs和Master可编程接口GPIF。在本方案中,选用了Slave FIFOs方式,异步读写。SlaveFIFOs方式是从机方式,DSP可以像读写普通FIFO一样对CY7C68013内部的多层缓冲FIFO进行读写。

具体的电路连接如图5所示。FLAGA、FLAGB和FLAGC是CY7C68013内部FIFO的状态标志,C6203B通过通用I/O口来获得FIFO的空、半满(由用户设定半满的阈值)和满等状态信息。C6203B对CY7C68013内部FIFO的选择,以及数据包的提交也是通过通用I/O口来实现。C6203B通过EMIF接口的CE2空间对CY7C68013进行读写操作。

工作过程为:DSP通过USB向PC发送数据时,首先查看空、半满和满这三个状态信号,然后向USB写入适当大小的数据,以保证数据不会溢出;PC机通过USB向DSP发送命令字时,USB通过中断方式通知DSP读取命令字。

3.3 应用程序设计

主机应用程序是主要实现从高速数据采集处理板该取处理后的数据、存储、显示处理结构以及向数据采集处理板发送控制命令。在Windows 2000下,我们使用的应用程序开发工具是VC++6.0。

4、系统工作原理

上电后,ADS5422一直工作,采样产生的数据是否存储到IDT72V2113中,由C6203B的DX0引脚状态来决定。C6203B进行初始化,外部扩展总线的XCE3设置为同步FIFO读操作模式。DMA通道0配置为每次传输1帧,每帧1024个半字,同步事件设置为外部中断4,触发极性为高电平,初始化定时器0,定时间隔为22ms。当外部同步信号到来时,启动定时器0,手动启动DMA通道0,同时设置DX0为低电平。

ADS5422采样产生的数据开始写入IDT72V2113,当定时器0中断到来时,设置DX0为高电平,关闭IDT72V2113的写使能,采样数据不再存储到IDT72V2113内。随着数据不断写入IDT72V2113,当其内部的数据量大于1023个半字时,IDT72V2113的将空标志信号(PAE)由低电平变为高电平,使得C6203B的外部中断信号有效,从而触发DMA传输,C6203B的DMA通道0通过外部扩展总线(XB)读取1024个半字的数据,存储于内部RAM中,传输结束后向C6203B发送中断,通知C6203B处理数据。

C6203B处理完数据后,通过USB2.0接口发送处理结果,然后重新启动DMA通道0,进行下一次DMA传输。如此循环,直到处理完所有数据。当下一个外部同步信号到来时,进行下一轮数据采集处理过程。

5、总结

本文详细介绍了基于USB2.0接口和DSP的高速数据采集处理系统的系统构成、硬件连接以及USB2.0驱动程序和固件程序的开发。经实际验证,系统运行可靠,是一种比较好的高速数据采集与处理的解决方案。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多