SRAM Buffer被分为两个区域,一般将General Purpose Buffer设为发送区,RX FIFO Burfer设为接收区,通过指针ERXST区分两个区域,通常将接收区设置较大以防止接收帧溢出。

[page]

2 系统硬件电路设计

2.1 网络控制器外围硬件电路

ENC424J600网络控制器外围硬件电路设计需要注意的几点有:ENC424J600的SPISEL引脚需要通过100kΩ电阻上拉至电源,这样系统上电时就能进入SPI模式,同时引出INT引脚作为接收中断使用;每个电源引脚与地之间都应连接一个电容,为更好地防止干扰在设计时加了两个电容,布线时使0.01μF电容更靠近电源引脚;RBIAS引脚需接一个12.4 kΩ的电阻到地;另外RD+、RD-差分信号处的接法与一般的网络控制器不同,它不是直接通过电阻接到电源上,需要特别注意。以太网接口则采用HR961160C,该插座集成以太网隔离变压器、LED灯于一体,同时是贴片式的,节约PCB制板空间。在PCB布线时需要注意的是RD+、RD-和TD+、TD-两对高频差分线的走线应对称并尽可能短。

ENC424J600外围硬件电路及HANRUN以太网变压器插座外围电路图如图2、图3所示。[page]

3 系统软件设计

软件的设计主要是移植LwIP协议栈,添加各串行通信接口的初始化程序,编写网络控制器底层驱动,编写上层应用程序。

3.1 网络控制器底层驱动实现过程

网络控制器底层驱动初始化程序放在low_level_init函数中,整个过程为:初始化SPI1接口,对网络控制器进行系统复位;设置发送、接收缓冲区指针;初始化PHY层为100 Mbase全双工模式,使能接收中断。网络控制器底层发送程序放在low_level_output函数中,整个过程为:将以太网包拷贝至SRAM buffer,设置发送起始地址;发送帧长,置高TXRTS位使能发送,直到TXRTS被硬件清零才能进行第二次发送。网络控制器接收程序放在low_level_input函数中,当接收中断发生时系统通过上层应用程序调用low_level_input函数。该函数主要内容为:读取PKTIF位以确定是否有以太网帧等待接收;设置接收指针地址,读取该帧的前8个字节,其中前两个字节为下一帧接收地址,第3、4个字节为这一帧的长度,申请当前帧长的缓冲区,将接收数据读入缓冲区,置高PKTDEC为下一帧接收做准备。

3.2 LwIP协议栈分析

LwIP协议栈可以在无操作系统的软件平台下移植,LwIP实现的重点是在保持TCP/IP协议主要功能的基础上减少对RAM的占用,因此它也适合在中低端的嵌入式系统中应用。LwIP主要是完成IP层和TCP/UDP数据传输层的任务,它与底层网络控制器的接口主要体现在etherneti f.c函数中。在以太网帧的接收过程中以太网数据包通过底层接收程序传至IP层,IP层判断是TCP数据包还是UDP数据包,送至相应数据传输层处理,数据传输层再将收到的数据传至用户应用程序。在以太网帧的发送过程中,用户程序选择是通过UDP还是TCP发送数据包,将数据包送至相应的传输层,再传至IP层,IP层再将数据传至底层,发送程序将数据发送出去。

3.3 系统软件流程

系统软件流程如图5所示。

软件主要完成初始化、等待接收以太网帧、通过串行接口将数据帧发送出去的任务。初始化包括创建netif网络接口、SPI1接口、网络控制器的PHY层、MAC层,使能接收中断、初始化TCP服务器端。初始化完成后,等待上位机软件TCP的客户端与底层软件的TCP服务器端建立连接。连接建立后整个系统就循环等待接收TCP客户端发送的以太网数据帧,当有以太网数据帧到达时,产生接收中断,接收到的数据帧从PHY层传到MAC层,再传到IP层,最终传到TCP层进行数据接收处理。应用程序收到处理过的以太网数据帧,处理相应的数据,根据数据传递的信息通过SPI2或CAN总线串行通信接口将信息发送出去,以实现相应的控制功能。

[page]

3.4 TCP/UDP上位机与系统通信

结语

文中介绍了利用ENC424J600网络控制器和LwIP协议栈实现以太网通信的过程,该系统不但体积小巧而且速度快、稳定可靠,具有良好的应用前景。

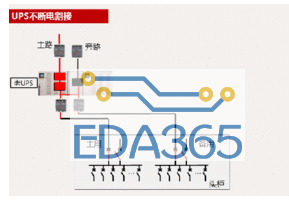

此系统目前已应用于网络转SPI通信来控制继电器板卡的测试设备中。该继电器测试设备称为MATRIX-RELAY(即矩阵继电器),每块继电器板卡上有46行×8列个继电器,共有5块继电器板卡,即46×8×5个继电器,通过打通该设备上的某一行或多行上的某两点来对待测产品进行相应的测试。测试员通过电脑上的上位机指定需要打开的继电器序号,向该系统发一帧网络数据,这帧数据包括需要打开的继电器属于哪块板卡、哪一行、哪一列等信息。通过该系统的处理,将数据转为SPI串行数据,再通过一系列移位寄存器的移位来控制相应继电器的打开从而达到测试产品某两端的目的。该测试设备在实际的运行中非常稳定可靠。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多