深耕于开发内存测试与修复技术的芯测科技(iSTART-Tek,简称 iSTART),宣布与南京邮电大学南通研究院合作,提供便捷版内存测试开发平台『EZ-BIST』以及相关课程培训,协助南京邮电大学相关系所学生在校时可以培养可测试性设计的设计概念和专业能力,在内存测试领域能更快速的与产业直接接轨也增加未来就业时的竞争力。

芯测科技业务发展部副总暨代理发言人张容诚表示,随着集成电路迈向更先进的技术节点(Process Node),加上 SoC 芯片的复杂度也越来越高,如何透过可测试性设计包含内存内建测试与修复来减少芯片的测试周期和成本,并在量产中控制产品品质(DPPM,每百万个产品中的不良率)变得越来越重要。芯测在访问客户的过程中,看到了越来越多客户有成立可测试性设计部门的需求,但苦于相关人力的缺乏。所以希望透过大学计划,跟各院校的电子、电机、资工与信息等相关系所合作,协助客户解决这样的问题。而与学界知名的南京邮电大学南通研究院展开合作是这个计划的重要起点,同时我们也有计划的跟更多学院展开相关合作的讨论,希望透过持续的与相关系所合作来提升芯测在产学合作方面的深度。

南京邮电大学南通研究院执行副院长蔡志匡表示,本次与业界知名的芯测科技(iSTART)合作只是一个开端,未来双方将在创新、研究和教育方面开展深度产学研合作,提升学生科技实践水平、拓展其科研经验,增强集成电路设计能力,为南通及周边地区输出受过良好培训的专业人才,促进区域产业转型升级。

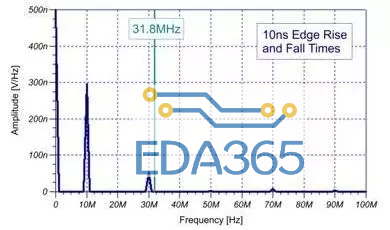

芯测科技是目前在提供内存测试与修复解决方案的领导厂商,提供各式内存包含 SRAM,DRAM,eFlash,MRAM/RRAM,MTP 完整的可测试性设计。『EZ-BIST 便捷版内存测试开发平台』是秉持着帮助开发者以更简单、更快速、更低成本的途径实现优化的内存测试电路的一套 EDA 工具。凭借高效能、低功耗可程序化暨管线式架构内存测试技术,从整体的芯片设计切入,透过易使用的图像化人机接口(GUI)设定相关参数及选项,全自动的辨识 SoC 设计中的内存并将其分群,并且具有完善测试算法、硬件架构共享、诊断信息纪录与设计电路自动整合等完整功能。让用户能轻易产生优化的内存测试电路的,大幅减少设计成本与时间,以提升测试良率、降低测试成本,提高产业竞争力。

APP下载

APP下载 登录

登录

热门文章

热门文章