1、最简单的接收端结构

|

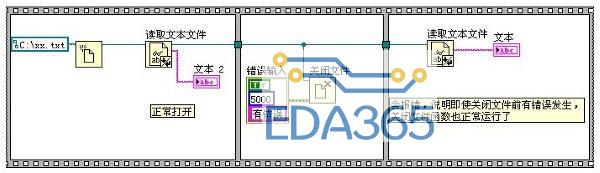

图1基本D触发器的锁存数据示意图

最简单的接收端可以看着一个D触发器,有一个时钟输入接口和一个信号输入接口及一个信号输出接口。输入时钟对D触发器和输入数据进行触发和采样后输出数据。如上图1所示为一个基本的D触发器锁存串行数据基本示意图。

一般低速信号接收端的结构和工作原理相对来说比较简单。且传输的信号速率也往往很低,信号即使经过较长的通道传输后也不会有太大的衰减,因此接收端出现问题的概率会小很多,所以一般5Gbps速率以下的信号的规范通常不会将接收端测试作为必选的测试项目。

2、典型高速串行数据的基本结构

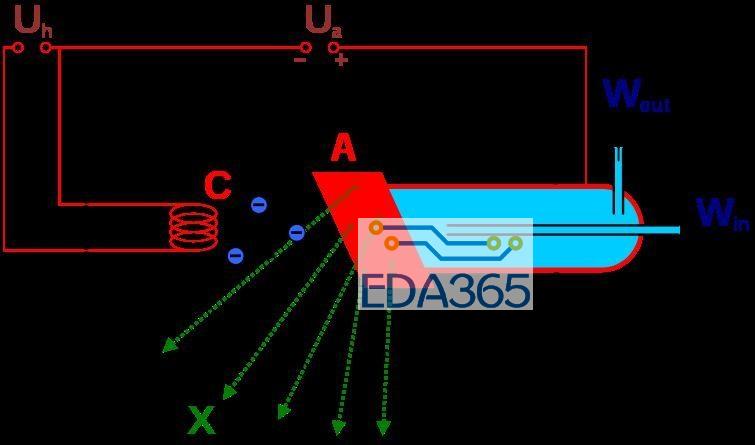

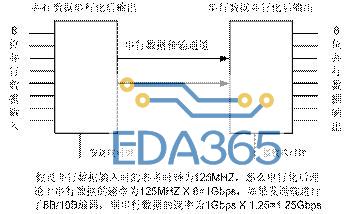

图2典型的并行/串行数据的基本传输结构

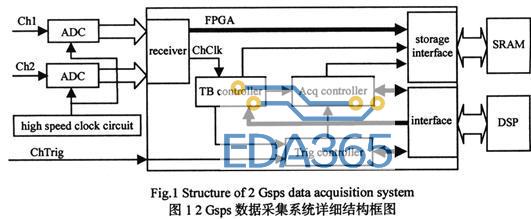

并行数据转换成串行数据并辅以相应的编码,可以以LVDS或者CML等差分电平的方式实现高速、高可靠的传输,传输通道结构也可实现极大的简化。从上述结构图中我们可以看出,串行数据传输链路中是没有专门的时钟信号传输的,那么接收端如何实现对串行数据的解串、解码呢?事实上接收端会有专门的CDR(Clock Data Recovery)电路用以从串行数据中恢复出时钟。因此,一个最典型的串行数据链路的发送端的内部结构至少应包括:串行化(Serializer)电路、8B/10B编码电路(通常在8B/10B编码电路之前还有一级Scramble编码电路以减小信号的高频谐波分量及信号失真);接收端应至少包括解串电路(Deserializer)、8B/10B解码电路、CDR时钟数据恢复电路等。

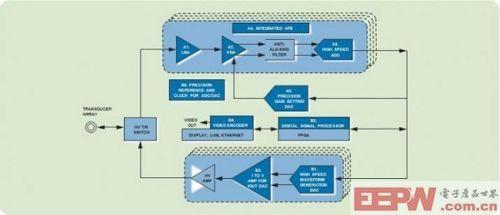

当串行数据的速率进一步提高,比如说数据速率达到5Gbps以上,如USB3.0,PCIE GEN3等,串行数据链路中各个组成成分都会影响到信号的质量。如传输线、接插件、阻抗不连续、芯片封装等,在实际应用中我们常会发现在接收端芯片管脚处测试得到的信号眼图已经接近闭合,眼图闭合的主要原因来自于高速信号传输过程中受到传输链路各组成成分的影响而导致的。为了改善信号眼图的质量,芯片端会采用一些补偿的措施,如在发送端采取预加重的方法对信号的幅度和边沿提前进行优化,来补偿高速信号通过传输链路后可能带来的损耗;而在接收端芯片中还可以使用均衡的方法来实现对信号的补偿。这样接收端和发送端的结构会变得更为复杂。如下图3所示,接收端有均衡器、时钟数据恢复电路、解串电路、8B/10B解码、Scramble解码、弹性缓冲器(Elastic Buffer,通过插入或者丢掉时钟对齐符号码来实现发送端和接收端的时钟速率的一致)等。

APP下载

APP下载 登录

登录

热门文章

热门文章