图1中环路滤波器的两个参数C1,C2计算式为:

式中:ts为采样周期。

阻尼系数为固定值通常取ζ=0.707,无阻尼固有频率ωn的取值根据锁相环频率捕获范围确定,可取为与要求捕获频率相近的值。由式(4)计算出C1和C2即完成理想二阶数字锁相环的参数设计。

[page]

2 直接数字频率合成

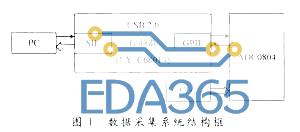

直接数字频率合成(DDS)用于实现锁相环的VCO。DDS的原理如图2所示。

DDS由相位累加器、正弦表、DAC和滤波器组成。相位累加器长度为N位,显然2N相当于360°(2π rad)。DDS是以系统时钟频率fs对相位进行等间隔的采样,每个系统时钟周期Ts输出频率fo的相位增量为FW×2π/2N。完成一整周正弦输出需要2π/(FW×2π/2N),即2N/FW个系统时钟周期,可以得到输出频率:

由式(5)可知,相位累加器的长度N越大,DDS的频率分辨率越高。如果将相位累加器全部字长作为正弦表的地址将会占用很大的存储空间,一般只选取最高的W位。这样既获得了高的频率分辨,又节省了存储空间。正弦表的输出经DAC变为模拟信号,再由滤波器滤除DAC采样时钟的谐波得到期望的输出频率fo。

目前DDS技术已经比较成熟,已有很多DDS芯片可供选持。AD9912是AnaLog Devices的高性能DDS器件,其系统时钟高达1 GHz,相位累加器高达48位。由式(5)可知其频率分辨优于4μHz,足够满足一般通信系统定时同步的要求。

3 基于DDS的定时同步方法

高速数据传输的数据速率为300 Mb/s,调制体制采用QPSK。QPSK兼顾了频率效率和带宽效率,是高速数据传输中应用最广泛的调制体制。锁相环的鉴相器采用Gardner算法。Gardher算法提取时钟误差独立于载波相位,即定时同步时不需先进行载波同步。Gardner算法每个符号只需两个采样点,即只要求采样速率是符号速率的两倍。QPSK的Gardner定时误差表达式为:

式中:y1(r),yQ(r)表示I,Q两路第r个符号判决时刻样点值;y1(r-1/2),yQ(r-1/2)表示介于第r个符号和第r-1个符号中间的样点值。

基于DDS的高速定时同步原理框图如图3所示。

中频输入与本振在正交解调器内混频解出QPSK的I,Q两条支路信号。QPSK每条支路的数据速率为其总速率的1/2,故I,Q的速率为150 Mb/s。ADC对I,Q两路分别采样,采样时钟频率为300MHz(支路数据速率的2倍),采样时钟由DDS产生。ADC采样后的信号送到FPGA进行处理,FPGA选为Xilinx公司Virtex-5系列中的XC5VSX95T,其内部丰富的DSP资源适合算法实现。在FPGA内,I,Q采样信号首先进行平方根升余弦匹配滤波,然后送到Gardner鉴相器提取相位误差。相位误差累加后以较低的100kHz速率送给环路滤波器进行更新。选ζ=0.707,ωn=100Hz,由式(4)可汁算出环路滤波器的参数C1和C2。环路滤波器输出的频率控制字送到DDS调整其输出采样时钟相位完成定时同步环路的闭环控制。

4 结论

定时同步是高速数据传输的一项关键技术。在对锁相环和DDS原理分析的基础上提出了基于DDS的高速定时同步方法,采用该方法设计了300Mb/s解调器进行实验测试,取得了满意的结果。基于DDS的高速定时同步方法也适用于更高速率的数据解调,为高速数据传输方案设计提供了参考。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多