SoC设计者在选择工艺技术时,常常不得不做出“红还是蓝”的决定。通常,必须在性能、功耗和面积之间做出选择,其中一个优先考虑,另一个次要优先考虑。然而,正如Mixel和NXP在最近的一篇论文中指出的那样,如果设计师考虑使用全耗尽绝缘体上硅(FD-SOI)工艺,那么他们可以同时满足更多的优势。这一点尤其正确,因为FD-SOI以工具支持和IP可用性的形式正在提供广泛的生态系统。

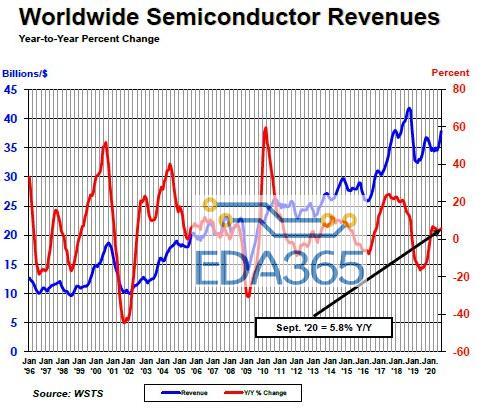

FD-SOI与体CMOS相比是一种利基技术,但随着物联网等应用对低待机功率和模拟与数字性能的新需求,FD-SOI的复兴可能正在开始。在Mixel高级工程总监Eric Hong和NXP Semiconductors产品线经理Nik Jedrzejewski撰写的题为“是时候再看看FD-SOI了”的论文中,他们指出FD-SOI具有独特的特性,是物联网的最佳选择。

Mixel和NXP合作为设计者提供了一种优于CMOS工艺的替代方案。本文重点介绍了利用Mixel的mipi d-PHY-IP的NXP i.mx7ulp平台。

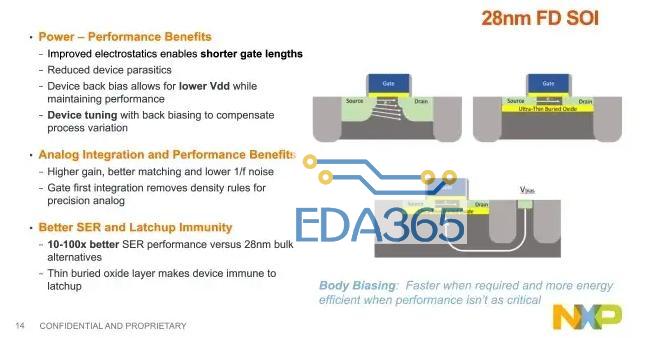

让我们看看作者对FD-SOI器件的性能特点有何看法。FD-SOI在整个晶体管下面放置了一层氧化物绝缘层,它使用了一个具有凸起源极和漏极材料的薄沟道。这种结构提供了许多有趣的特性,可以用来改进芯片设计。这种配置减少了寄生和短沟道效应。

在体CMOS中,源极、漏极和衬底之间存在寄生电容。此外,在体CMOS中,栅致漏的漏效应(GIDL)和漏致势垒的降低效应(DIBL)分别对阈值电压和高漏电压关断产生严重影响。另一方面,在FD-SOI中,埋置的氧化物(BOX)层屏蔽了源极和漏极,并允许更薄的沟道,提高了栅极的关断能力。栅电容和寄生电容的降低意味着峰值功率和动态功率的降低,跨导和ft的提高。

FD-SOI优势

也许FD-SOI最有趣的特性是结下衬底的体偏压可以很容易地应用。这种体偏压甚至可以根据当时需要的工作特性进行动态修改。为了改善泄漏电源,可采用反向阀体偏置(RBB)。作者报告说,使用这种技术,泄漏可以减少50倍。

通过施加正向体偏压(FBB),可以降低阈值电压,从而提高性能和更高的栅极驱动(Vdd-Vt)。作者提到了使用1V电源时性能改善超过60%的情况。Mixel观察到在快速转弯处(Fast Corner)的设计可以节省50%的电力。同样的设计在典型拐角处(Typical Corner)的功率降低了14%。这是通过将片上设备的W/L降低55%来实现的。体偏压也可以用来补偿模具之间的变化,以提高产量。

本文还详细介绍了FD-SOI在模拟设计中如何改善晶体管的许多性能特性。FD-SOI可以为寻求提高功率、性能、面积和产量的设计提供了不止一个,而是许多优点。

NXP与Mixel合作,为基于FD-SOI的SOC设计搭建了一个非常引人注目的平台。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多