据报道,目前最先进的技术应该是使用硅通孔的3D芯片堆叠,几乎主要的半导体公司都在研究这种技术。

去年举行的国际固态电路会议上,三星公开宣布了其2.5D技术,据称这种2.5D技术非常适合位于在系统级芯片上进行带硅通孔和微凸块的堆叠式DRAM裸片。三星准备把这种技术用在1Gbit移动DRAM产品上,并计划在2013年使移动DRAM容量提高到4Gbit。

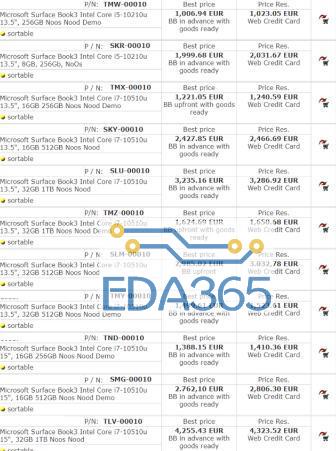

赛灵思公司推出了一种2.5D封装工艺的多FPGA解决方案,这种工艺可在硅中介层上互连4个并排且带微凸块的Virtex-7FPGA。目前,台积电也正在生产这种硅中介层,使用硅通孔技术重新分配FPGA的互连,台积电已承诺将在2013年向其代工客户提供这种转换技术。

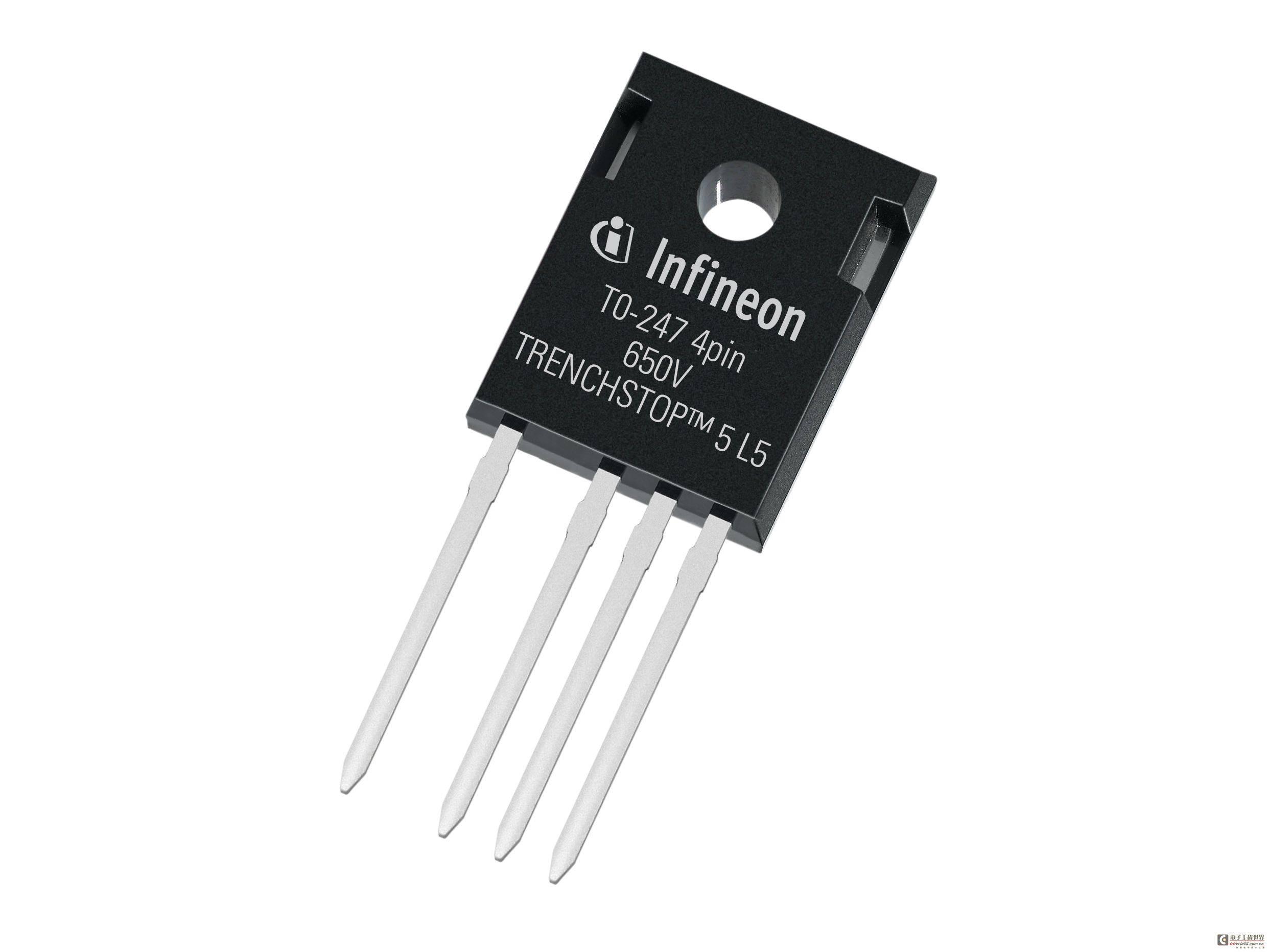

还有多家公司目前都在进行3DIC生产技术的研发。TezzaronSemiconductor公司为其钨硅通孔工艺提供3DIC设计服务已经有多年。Tezzaron的FaStack工艺可以从薄至12微米晶圆上的异质裸片制造3D芯片。这种工艺具有针对堆叠式DRAM的宽I/O特性,其亚微米互连密度高达每平方毫米100万个硅通孔。

3D技术可以给芯片设计带来许多新的想法。设计师必须采用不同的思维方式,以创新的方式组合CPU、内存和I/O功能,这是每样东西只能在邮票大小的面积上并排放置不能做到的。

据有关资料,生产3DIC的技术并不是很新的技术,堆叠芯片想法本身可以追溯到1958年颁发给晶体管先驱WilliamShockley公司的早期专利。从那以后,业界已经使用了许多堆叠式裸片配置方案。比如,将MEMS传感器堆叠在ASIC之上,或将小的DRAM堆叠在处理器内核上等。

去年获得EETimes年度ACE创新大奖的ZviOr-Bach则认为3DIC设计师需要从硅通孔技术过渡到超高密度的单片3D技术。BeSangInc声称正在制造无硅通孔的单片3D内存芯片原型,并有望于2012年首次亮相。

据报道,目前有许多半导体协会都在研究制定3D技术标准。国际半导体设备与材料组织(SEMI)有4个小组专攻3DIC标准。其三维堆叠式集成电路标准委员会包括SEMI成员Globalfoundries、惠普、IBM、Intel三星和UnitedMicroelectronicsCorp.(UMC)以及Amkor、ASE、欧洲的校际微电子中心(IMEC)、亚洲工业技术研究院(ITRI)、奥林巴斯、高通、Semilab、东京电子和赛灵思公司等。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多