摘要:介绍了QDPSK信号的优点,并分析了其实现原理,提出一种QDPSK高性能数字调制器的FPGA实现方案。采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、逻辑选相电路、四相载波发生器等4大模块,用原理图输入、VHDL语言设计和调用PLL核相结合的多种设计方法,分别实现了各模块的具体设计,并给出了其在QuartusⅡ环境下的仿真结果。结果表明,基于PLL的QDPSK调制器,设计简单,便于修改和调试,性能稳定。

关键词:QDPSK;串/并变换;数字调制器;FPGA

FPGA器件(Field Programmable Gate Array)是八十年代中期出现的一种新概念。利用FPGA技术设计的产品具有重量轻、体积小、速度快、保密程度高、功耗低等特点,极大地提高了产品的性价比和竞争力,大大缩短了设计周期,减少了设计费用,降低了设计风险。

数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制。这种调制的最基本方法有3种:振幅健控(ASK)、频移键控(FSK)、相移键控(PSK)。根据所处理的基带信号的进制不同,它们可分为二进制和多进制调制(M进制)。多进制数字调制与二进制相比,其频谱利用率更高。其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用较广泛的一种调制方式,该方式广泛应用于卫星通信、电缆调制解调、视频会议系统、蜂窝电话和其他数字通信领域。然而QPSK信号在解调的时候易产生相位模糊问题,即可能会产生0、π/2、π、3π/2 4种相位模糊。解决的方法就是采用四进制差分相位键控(QDPSK),对于相对移相,基带信号是由相邻两码元相位的变化来表示,它与载波相位无直接关系,即使采用同步解调也不存在相位模糊问题,因此在实际设备中相对移相得到了广泛运用。本文研究了基于FPGA的QDPSK调制电路的实现方法,重点阐述了串/并变换、差分编码、四相载波发生器等电路的原理与实现方法,并给出了其在QuartusⅡ环境下的仿真结果。

1 QDPSK调制原理

1.1 四相绝对移相键控(QDPSK)

相对调相(相对移相),即DPSK(Differential Phase Shift Keying),也称为差分调相,这种方式用载波相位的相对变化来传送数字信号,即利用前后码之间载波相位的变化表示数字基带信号。在QDPSK信号中,若以前一双比特码元相位作为参考,并令△φ为当前双比特码元的相位差,则可得到双比特码元与载波相位变化关系如表1所示,从表中可以看出,A方式中,载波相位互差π/2,实现比较容易,因此采用A方式。

1.2 QDPSK的调制方法

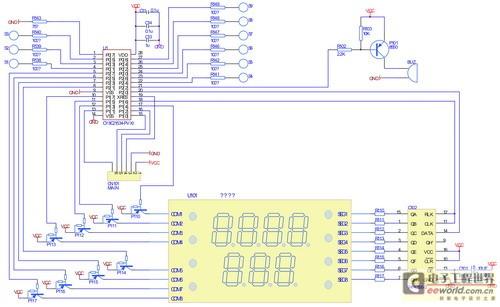

QDPSK的产生方法可采用调相法和相位选择法。图1为相位选择法产生QDPSK的原理框图。在图1中,四相载波发生器分别送出调相需的4种频率相同、相位互差π/2的载波,输入二进制数字基带信号经串/并变换为四进制数字基带信号,经差分编码变为四进制差分码,逻辑选相电路根据差分编码后的双比特码cd,每隔时间间隔T选择输出其中一种相位的载波。虚线内的信号均为数字信号,可直接利用FPGA来实现ODPSK调制。

2 QDPSK数字调制器的实现

2.1 串/并转换、相位选择的实现

顺序输入的二进制信息经过串/并变换器,变换成速率减半的双比特序列,可采用2个D触发器来实现,其原理如图2所示。其中DFFinst和DFFinst3构成一个两位移位寄存器,将串行输入信号变成并行输出信号;DFFinst4和NOTinst8构成二分频器,实现速率减半;DFFinst1和DFFinst2为锁存器,使信号同步输。图3为串/并变换器s-p的仿真结果,其中AB为变换后的双比特码元。由图可以看出,当输入DataAB为01010101时,在延时约80 ns后,输出DataA为0000。DataB为1111。逻辑选相电路主要实现在4种不同的相位中选择一种输出,即四选一电路,电路结构简单,用VHDL语言或组合逻辑电路均可实现,这里不作祥细介绍。

2.2 差分编码器的实现

差分编码器的功能就是实现绝对码变换为相对码,在相码中,1、0分别用相邻码元电平是否发生跳变来表示。若用相邻电平发生跳变来表示码元1,则称为传号差分码,记做NRZ码。绝对码一相对码之间的关系为:

由表达式(1)可得到其变换电路如图4所示。

采用VHDL设计的主体代码如下:

经编译后,可生成如图5所示元件,元件名为QDPSK_PL,其中clk为系统时钟;start为同步信号,高电平有效;datain_a和datain_b分别两路输入信号;dataout_a和dataout_b分别两路输出信号,其波形仿真图如图6所示。由图6可以得到:当start为低电平时,两路输出信号都为0;当start信号为高电平时,对输入信号(datain_a)有:datain_a=011111111001,此时dataout_a=010101010001,对输入信号(datain_b)有:datain_b=011110111101,此时Dataout_b=010100101001,由此可以得出,元件QDSP_PL实现了由绝对码到相对码的变换。

2.3 四相载波发生器的实现

由图3可知,四相载波发生器主要产生4种频率相同、相位互差π/2的载波信号。实现四相载波有很多种不同方法。可先由振荡电路产生一定频率的信号,再利用RC移相电路得到不同相位的波形;也可以利用NCO的Implementation项目设置启用相位调制功能,通过设置相位调制精度输出4种不同的相位。该系统利用QuartusⅡ5.2内部的PLL直接产生clk0和elk1两路频率相同、相位相差π/2的信号,再用2个非门分别对clk0和clk1取反,得到clk2和clk3。这样就可以实现四相载波发生器的功能,其原理图如图7所示,图8为输出波形仿真图。

把上述各部分所生的symbol在QuartusⅡ5.2提供的BlockDiagram/SchematicFile中用Graphic Editor编辑连接起来,就形成了图1的虚线所示的部分,编译后进行整体模块仿真,经过器件编程,可将整体模块程序烧写到合适的FPGA芯片中,再配以相应的D/A器件及其他外围电路,调试后即完成设计。

3 结束语

用FPGA来实现QDPSK信号发生器,电路简单,设计灵活,便于修改和调试,可靠性高。另外,Ahera公司的QuartusⅡ5.2应用软件具有较强大的开放性和综合性。它可以利用其他各种EDA资源以及先进的设计方法,使其功能更加完善和强大。它可以实现从简单的接口电路设计到复杂的状态机,甚至“Sys-temon Chip”。它的可编程特性带来了电路设计的灵活性,缩短了产品的“Time ToMarket”。

本文作者创新点:基于PLL提出了一种QDPSK的FPGA实现方案,采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、逻辑选相电路、四相载波发生器等4大模块,用原理图输入、VHDL语言设计和调用PLL核相结合的多种设计方法,分别实现了各模块的具体设计,该方案极大地简化了系统的设计过程和难度,甚至可做到不需要编写任何程序实现QDPSK调制器的设计。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多