控制器局域网(CAN)标准不断发展,正用于车载和工业网络之外的许多新应用。支持它的微处理器变得普遍且价格低廉,并且开源协议栈让其非常容易访问,同时也容易添加至新系统。有许多CAN板可用于BeagleBone (Capes)、Stellaris (BoosterPacks)、Arduino (Shields)和其他微处理器开发平台。当设计人员的系统上电却不能工作时,应该怎么办呢?本文为您介绍一种对CAN物理层进行调试的较好工程方法。我们将介绍基础调试步骤,并说明一个CAN物理层应有的性能,以及找出问题的一些小技巧。

调试基础知识

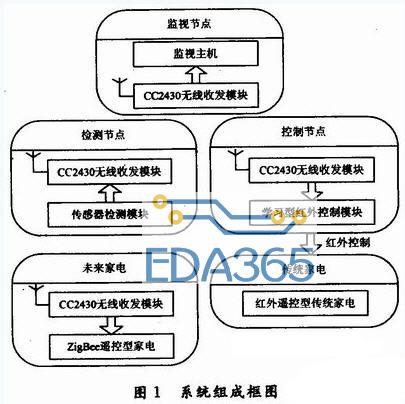

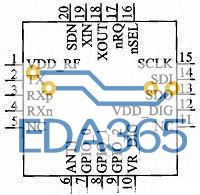

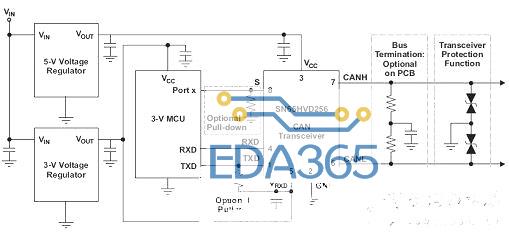

ISO11898-2和ISO11898-5规范详细说明了高速CAN物理层即收发器。掌握CAN物理层的基础知识以后,利用简单的调试工具便可迅速地找出常见问题。所需的基本实验室工具为示波镜、数字万用表(DMM)和一个电源。如果想要深入了解问题,则需要更高精度和更复杂的工具。这种问题已非本文讨论的范畴,但是这里介绍的基础知识可帮助确定问题所属类别,以及进一步调试所需的其他工具。一个由 TI 组装的CAN演示系统以及TI的SN65NVD255D评估模块(EVM)1,用于演示硬件。另外,我们还使用了其他一些东西,例如:CAN连接器外接头电缆和芯片钩(抓住收发器引脚,让其连接至电缆,以更加容易地连接示波器指针,如图1所示)。

图1:CAN物理层调试基本工具

连接检查

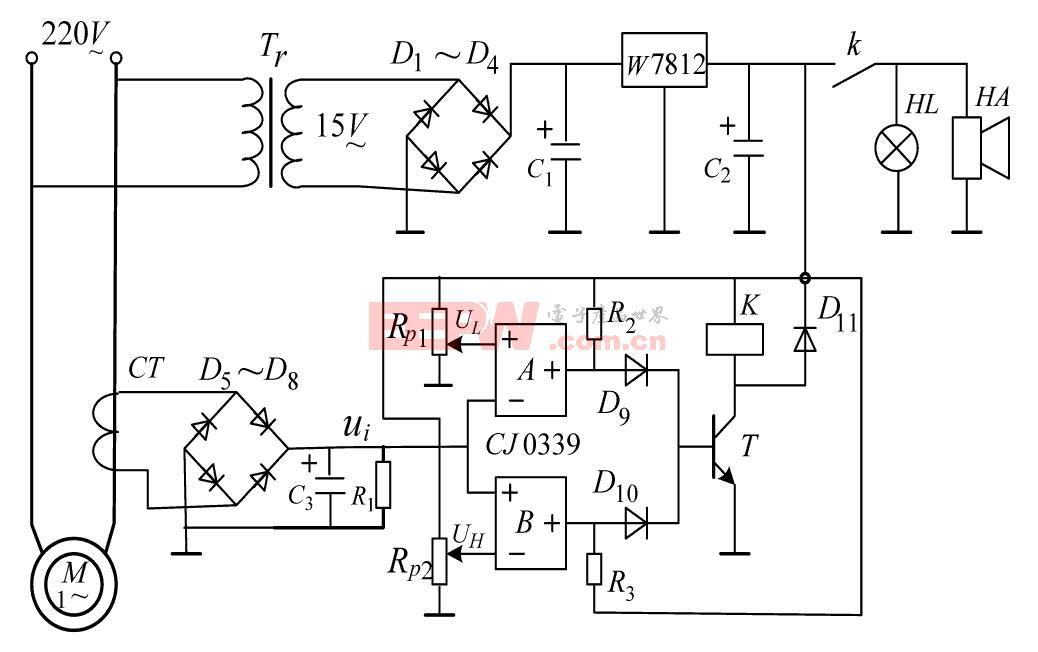

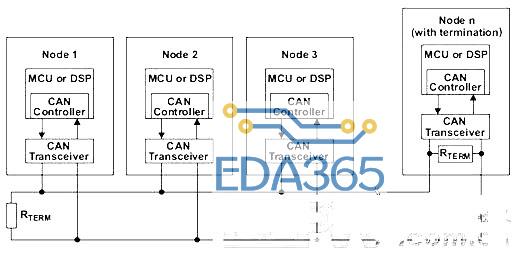

开始调试对话时,使用DMM确认印刷电路板(PCB)上连接如我们所预计的那样—系统未上电。这看似很基础,但令人吃惊的是,这个简单的方法却解决了许多简单问题。所有人都会认为原理图、布局和制造工艺没有问题,但不幸的是,它们有时却并不如人愿。子插件板位置错误、虚焊和错误端接或者连接的电缆,都是一些常见问题。利用DMM电阻设置来确认所有线路和连接均正确。图2所示CAN应用的简易原理图用作参考。

图2:CAN应用简易原理图

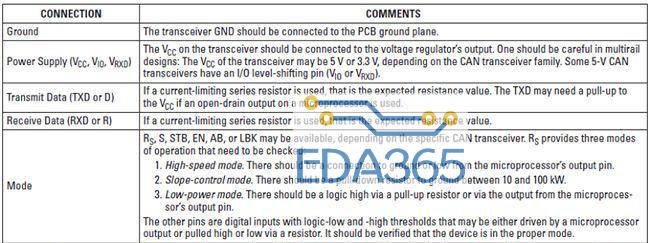

表1列举了需要检查的PCB和网络连接。收发器引脚和PCB上其他相关连接之间的电阻应为0Ω,除非设计使用表注里介绍的一些选项。例如,限流串联电阻器、总线端接电阻器或者数字I/O的上拉或下拉电阻器。

表1:PCB和CAN收发器连接总结

总线端接检查

大多数CAN标准均规定使用一条单双绞线(有或者无屏蔽层),其特性阻抗(Z0)为120Ω。应使用与线路特性阻抗相同的电阻器来端接电缆两端,以防止信号反射。端接可以为电缆上总线端的单120Ω电阻器,如图3中CAN总线左侧所示;或者,它也可以位于某个端接节点内,如图3右侧所示。不得将端接电阻从总线移除。如果CAN端接电阻负载不存在,则信号完整性会受到影响,并且无法满足比特计时要求。如果总线共模电压滤波和稳压理想,则使用分裂端接,如图2所示。在该图中,每个电阻器均为60Ω,而分裂电容器范围为1 nF到100 nF,具体取决于共模滤波器所需的频率。2CANH到CANL的测得电阻应介于45Ω到65Ω之间,以达到CAN标准、两个端接电阻器的并联阻抗以及并联节点输入电阻的容差。应根据可能碰到的极端故障状态(通常为系统接地的电源电压)来确定端接电阻器的额定功率。

图2:CAN应用简易原理图

电源检查

在系统上电以前,应首先检查CAN收发器的一个或者多个电源。根据所使用的收发器类型,VCC应为3.3V或者5V。不管您相不相信,在一些情况下,丢失VCC确实为问题的根本原因。因此,我们应确保VCC存在于收发器的VCC引脚上。只需检查DMM,便可确认有电源存在。必须注意电源短路接地(不幸的是,该引脚就在VCC引脚的旁边)。

显性状态(60Ω总线负载时约为60mA)和隐性状态(10mA)之间所需电流(ICC)差约为50mA。显性总线状态期间端接电阻差分电压的产生需要这50mA的电流差,并且其随总线负载变化而变化。DMM还可用在电流模式下,以验证预计ICC电源电流。由于CAN的开关性质,DMM测得的电流伪平均读取值。

建议本地旁路电容器至少应为4.7μF,以确保总线状态转换期间有足够的电源缓冲。否则,收发器的突入电流可能会引起明显的电压电源纹波。我们可以使用一个示波器来验证电源电压是稳定,还是随着总线状态变化而变化。转换期间,最好不要让收发器“饥饿”。收发器受到其限流的保护,但是,当收发器试图驱动总线至显性状态时,如果其中一条总线短路至电源或者接地,则电源电流极高。如果电压调节器无法提供这么多的电流,则电压电平降至收发器规格范围以下,甚至可能会低至触发收发器的欠压锁定状态。

电容器相关文章:电容器原理

万用表相关文章:万用表怎么用

上拉电阻相关文章:上拉电阻原理 双绞线传输器相关文章:双绞线传输器原理

APP下载

APP下载 登录

登录

热门文章

热门文章