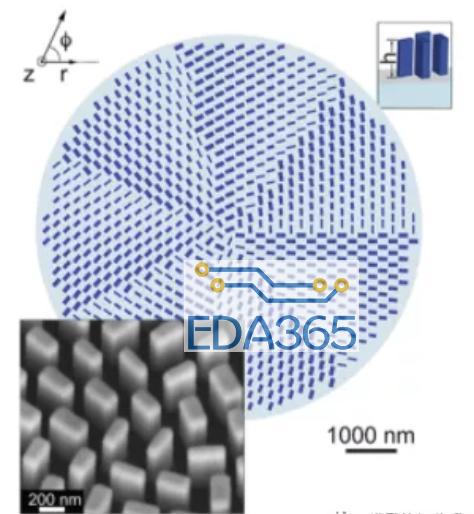

22nm以后的晶体管技术领域,靠现行Bulk MOSFET的微细化会越来越困难的,为此,人们关注的是平面型FD-SOI(完全空乏型SOI)元件与基于立体通道的FinFET。由于这些技术都不需要向通道中添加杂质,易于控制特性的不均现象,因而成了22nm以后晶体管技术的有力候选。而且前者还具有能够采用与此前相同的电路布局进行设计的特点。后者虽要求采用新的电路布局及工艺技术,但有望比前者更加容易实现微细化(高集成化)。两种技术以各自特色为宣传重点,开始激烈争夺新一代技术的宝座。在 “2010 Symposium on VLSI Technology”(2010年6月15~17日,在美国夏威夷州檀香山举行)上,似乎为了显示人们对二者的关注度之高,相关企业及团体就FD- SOI元件发表了9篇论文,就FinFET发表了4篇论文。

采用ARF光刻技术实现基于FinFET的超小SRAM单元

在2009年举行的“2009 IEDM”上,采用FinFET技术实现0.06um2或者0.039um2单元面积的超微细SRAM亮相。但是,这些产品都利用了电子束(EB)直描技术,实用化方面还存在课题。此次,美国IBM、美国GLOBALFOUNDRIES、东芝及NEC电子(现为瑞萨电子)组成的小组发布了以现行ArF光刻技术实现0.063um2超微細SRAM的极具影响力的研究成果(论文序号:2.2)。通过采用Sidewall Image Transfe技术,实现了40nm的Fin间距,解决了基于FinFET的SRAM的另一课题——因使用多个Fin而导致面积增大的问题。同时,还实现了80nm这一全球最小的栅极间距。作为实现超微细SRAM的技术,这一成果给人FinFET更为出色的强烈印象。

在Bulk底板上混载SOI及块状硅元件

要实现最尖端SRAM,易于控制特性不均现象的FD-SOI元件可发挥威力。不过,ESD保护电路及功率MOSFET等需要较大电流的外围电路沿用块状硅元件比较理想。从这一角度来看,二者的混载技术备受期待。在“2009 IEDM”上,多家企业发布了采用SOI底板、混载FD-SOI及块状硅元件的混载技术。

意法半导体(STMicroelectronics)、法国IMEP-LAHC及法国CEA-LETI组成的小组发布了在成本低于SOI底板的块状硅底板上混载FD-SOI与块状硅元件的技术(论文序号:6.2)。这是一项可实现低成本微细SoC的值得关注的技术。此次,FD-SOI元件领域通过在硅底板上使SiGe及Si固相生长,然后除去SiGe层并嵌入氧化膜,实现了局部SOI。在局部SOI上制作的FD-SOI元件的特性偏差在此前发布的产品中为最小水平(Avt=1.2mV um)。实证结果表明,在块状硅底板上制作的ESD保护电路可充分满足实用需求。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多