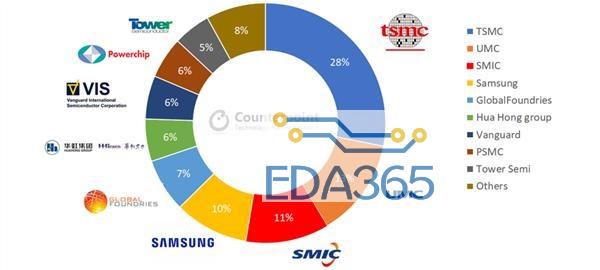

晶圆代工龙头台积电大动作启动人员扩编,为因应苹果订单落袋、主力客户赛灵思、超微等积极朝向先进IC制程迈进,台积电近期从日月光、矽品及力成等封测业挖角,成立逾400人的封测部队,全力挥军3D IC高阶封测市场、力拓版图。

据了解,台积电当初争取苹果A5处理器,即因后段封测布局不如三星而败阵,如今大动作布建3D IC封测部队,似乎透露台积电争取苹果新一代处理器订单已胜券在握。台积电发言系统昨(12)日则强调,不针对个别客户接单情况做评论。

据了解,由于苹果订单可望落袋,加上台积电主力客户包括赛灵思、超微、辉达、高通、德州仪器、迈威尔、Altera等,积极朝2.5D IC设计迈进,台积电为满足客户需求,正加速进行人员扩编行动。

近期台积电已直接从日月光、矽品及力成等封测大厂挖角,估计这批高阶封测研发人员已达420人,且还在扩充中。

近来在高阶制程上,台积电不惜砸重金扩产。此外,台积电为超越摩尔定律,由共同营运长暨执行副总蒋尚义领军的研发团队,独立发展高阶封测技术,将改变台湾半导体产业多年来上下游垂直分工的生产模式。台积电认为,目前3D IC仍有很大的难度,初期将先切入以矽中介层(interposer)为架构的2.5D IC封装。

封测业研判,从台积电扩扩编封测人员的行动及时程来看,订单掌握度似乎优于预期,预估明年第2季会有不错成效,对封测双雄将带来冲击。

阅报秘书/3D IC技术

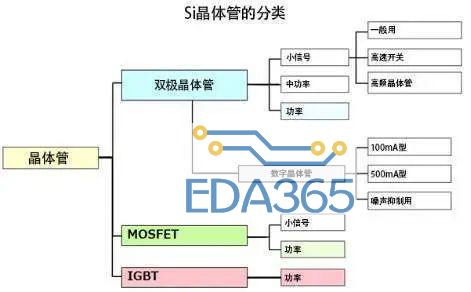

封测厂商将不同功能的芯片,以并排的方式整合成1颗,就是所谓的2D IC。3D IC则是更进阶的技术,业者将不同功能的芯片,用垂直堆叠方式,然后用矽钻孔(TSV)技术,将不同芯片的电路整合,有效缩短金属导线长度及联机电阻,就象是在平地上盖房子一样。由于减少芯片面积,使得3D IC具有低功耗、高整合度及高效能等特性,符合电子产品追求轻薄短小的新趋势。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多