摘要:本文设计了一种低电压、恒定增益、Rail-to-Rail的CMOS运算放大器,整个电路采用标准的0.6um CMOS工艺参数进行设计,并经过HSPICE工具仿真,在3V的单电源工作电压情况下,静态功耗约为9.1mW,当电路同时驱动20pF电容和500Ω电阻的负载时,电路的直流增益达到62dB,单位增益带宽达到18MHz,相位裕度为50o。

关键词:模拟集成电路;CMOS;运算放大器

引言

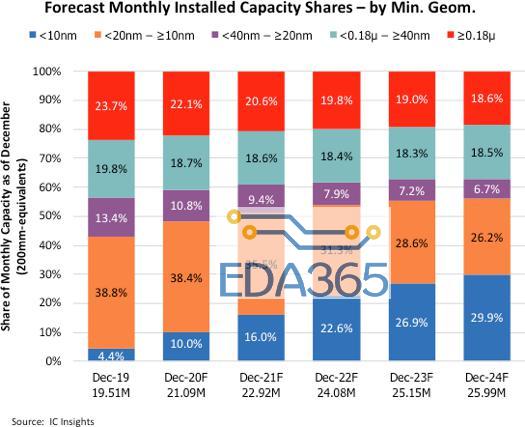

随着信息技术和微电子制作工艺技术的高速发展,器件的特征尺寸越来越小,由此构成的集成电路的电源电压也越来越低。1997年,半导体工业协会曾对未来十年CMOS电路的电源电压发展趋势作了预测,如图1所示。预计未来十年集成电路的电源电压将降至1.5V,甚至更低。

形成这种发展趋势的原因很多。其中主要有以下三方面原因:1、随着集成制作工艺的发展,器件的特征尺寸将逐渐减小,相同工作电压下小尺寸器件所承受的电场将逐渐增高,器件工作的安全性要求迫使工作电压必须相应降低,而电路集成规模或集成密度逐步增大的事实,导致大功耗、大发热量的芯片出现,同样要求采用降低电源电压来降低功耗。2、便携式电子装置的迅速发展及其呈现出的广阔市场,可植入人体的微功耗医疗电子部件的广泛应用等市场需求是对低电压电路的有力牵引。3、全球兴起的绿色环保——低能耗要求亦是发展低电压电路的重要动力。

虽然数字化处理技术已经广泛应用于电子设备中,然而电子设备的原始信号均来自现实世界,如电磁记录、扬声器、麦克风、CCD、LCD、无线调制器和解调器等,它们所产生的信号都为模拟信号,这些信号实现数字处理前必然要先经过模拟信号处理(比如放大、A/D转换等),同时数字化处理后的信号作用于现实世界时仍需还原为模拟信号(比如D/A转换、功率放大等)。因而即使在数字技术十分成熟的今天,模拟信号处理技术仍是无法回避,不能忽视的。而从集成技术的角度来看,单片数字系统集成制作的困难已成为过去,集成能力的进一步提高,提出了完整的电子系统集成,即包含数、模混合信号处理的片上系统(SoC)的要求。CMOS已是当今高密度集成的主流工艺,因此,低电压CMOS模拟电路的设计研究已成为完整意义上的SoC的关键技术。

运算放大器是模拟集成电路中的一个重要模块,随着电源电压的降低,传统的运算放大器结构已经不能满足设计指标的要求,近十年来,各种新结构的低电压运算放大器已经大量涌现出来。

本文设计了一种低电压、恒定增益、Rail-to-Rail的CMOS运算放大器结构,这种结构具有以下特点:1)具有Rail-to-Rail的输入和输出;2)在整个共模输入范围内具有恒定的增益; 3)具有驱动低阻抗的能力; 4)具有较大的增益带宽乘积等等。

运算放大器的输入级

低电压Rail-to-Rail运算放大器的设计难点集中在输入级部分,因为输出级可以采用简单的AB类输出级来完成。

为了得到Rail-to-Rail的共模输入电压范围,可以采用互补输入级的结构,如图2所示。NMOS输入对在高的共模输入电压范围内导通,即

Vin,cm>Vss+Vgs,n+Vds,n (1)

而PMOS输入对在低的共模输入电压范围内导通,即

Vin,cm>Vdd-Vgs,p-Vds,p (2)

从(1)(2)式中可以明显的看出,当共模输入电压范围处于中间值时,NMOS和PMOS输入对将同时导通,这也就意味着这个区间的输入级电流将增大一倍,根据下式:

其中K=μpCox(W/L)p=μnCox(W/L)n

所以互补输入级的跨导也将增大一倍,进而导致运算放大器的增益在整个共模输入电压范围内不是恒定的,如图3曲线1所示。

本文设计了一种具有恒定跨导的互补输入级结构,该结构思路简单并且有效地解决了上述互补输入级跨导变化的问题,如图4所示。

从上面的分析得知,为了使图2所示的输入级结构在整个共模电压范围内保持跨导一致,那么对应于高和低的共模输入电压范围内的跨导就必须增大一倍,又根据式(3),电流IDSQ与Gm呈平方根的关系,所以相应的尾电流就必须再增加三倍,图4结构正是基于这个原理之上的。

M1、M2和M3、M4分别组成PMOS、NMOS输入对,Iref1=Iref2=Iref提供相同的尾电流,M7、M8和M9、M10分别组成两个1:3的电流镜,M11、M12是两个电流开关管,偏置电压Vb1=Vb2=1.3V。因此,在共模输入电压从Vss到Vss+1.2V时,PMOS对M1、M2导通(M3、M4截止),同时M12导通(M11截止),Iref2通过M12到达1:3的电流镜M7、M8,M8的电流加上Iref1的尾电流,正好使电流增大到四倍,也即跨导增大到两倍;在共模输入电压从Vdd-1.2V到Vdd时,M3、M4导通(M1、M2截止),Iref1通过M11到达1:3的电流镜M9、M10,M10的电流加上Iref2的尾电流,也正好使电流增大到四倍,即跨导也增大到两倍;在共模输入电压从Vss+1.4V到Vdd-1.4V时,PMOS对和NMOS对同时导通,而电流开关管M11、M12截止,每个输入对的电流都等于Iref。

图3曲线2所示为上述互补输入级结构中共模电压与跨导的关系,从图中可以看出跨导在整个共模输入电压范围内基本保持不变,只是在两个过渡区有大约15%的浮动,这是由于NMOS管和PMOS管不完全匹配造成的。

运算放大器电路整体结构与仿真结果

运算放大器电路整体结构如图5所示,它由上面讨论过的输入级、中间的求和电路以及输出驱动器组成,其中输出驱动器由一个交叉级和一个输出级组成。 整个电路采用标准的0.6um CMOS工艺参数进行设计,并经过HSPICE工具仿真,得到如图6、图7所示的频率响应曲线。

整个电路在3V的单电源下工作,静态功耗约为9.1mW,。当电路同时驱动20pF电容和500Ω电阻的负载时,电路的直流增益达到62dB,单位增益带宽达到18MHz,相位裕度为50o。

结语

本文设计了一种低电压、恒定增益、Rail-to-Rail的CMOS运算放大器,输入级采用互补差分输入级结构,通过电流开关控制原理使放大器在整个共模输入电压范围内保持恒定的增益,输出级采用带有弥勒补偿的互补共源输出结构,得到Rail-to-Rail的对称输出摆幅。电路基于0.6um标准的CMOS工艺参数进行设计,并经过HSPICE工具仿真,得到了很好的性能。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多