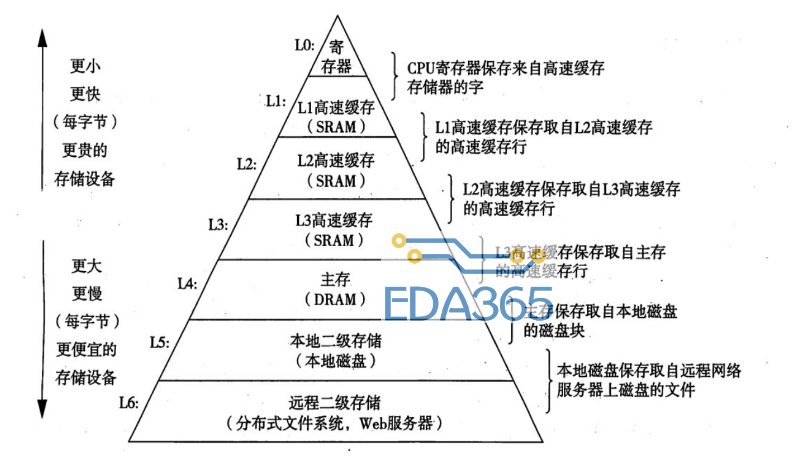

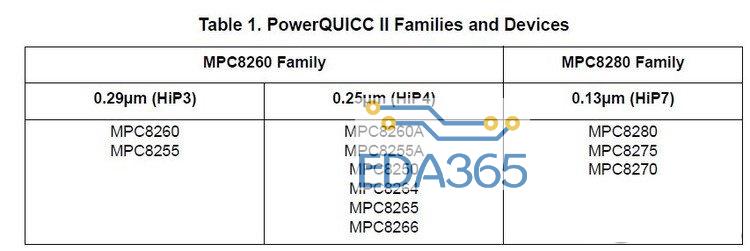

保证存储器中数据的完整性是存储系统设计的一个重要因素。两个主要的方式用于完成这个任务:校验和纠错码(ECC)。传统上,奇偶校验是用的最为常见的手段,但是奇偶校验只有检测一位错误的能力且没有纠错能力。在数据完整性方面ECC是一种更为综合的手段用于探测和纠正单比特错误以及探测双比特错误。本论题主要讨论PowerQUICCII数据错误保护机制。飞思卡尔公司的以下产品都属于PowerQUICCII的家族范畴。

1 奇偶校验基础

PowerQUICCII 对60X总线以及局部总线都能进行奇偶校验,这两者能够同时的并且独立的完成。

图一展示了奇偶校验的原理构成。0.29um工艺的设备(HiP3)DPRAM不支持任何的奇偶校验。0.25um(HiP4)和0.13(HiP7)设备一些奇偶校验能力得以增强。

当PowerQUICCII执行一个存储器写操作,他会产生一个奇偶校验/ECC。奇偶校验和数据一起存储在外部的存储器中。对于这种操作,PowerQUICCII 不会执行校验比较并且也不会产生校验错误。当PowerQUICCII执行一个存储读操作的时候,外部存储器同时驱动数据和校验位。PowerQUICCII校验逻辑计算当前读入数据的校验数据并且和从外部存储器中读入的校验位进行比对。两者间任何的失配都会产生一个校验错误。那么PowerQUICCII 就会依据程序报告该类错误信息。

PowerQUICCII支持3种类型的校验:一般,读-调整-写,ECC。校验方式在每个BANK的BRn[DECC]进行设定。每个bank可以有不同的校验模式,或者可以设置为无校验。对于一般校验或者读-调整-写校验,用户可以通过BCR[EPAR](对于60X总线),或者BCR[LEPAR](对局部总线)选择是奇校验还是偶校验。这两比特数据是全局的并且应用的所有的60X或局部总线上的BANK。ECC算法仅用于64比特数据。存储器数据宽度必须为64位的时候才能用ECC模式。

在存储控制器中产生并检查校验。603e核有自己独立的校验逻辑,通过HID0[EBD]它必须被禁止。校验错误通过MCP信号报告到603e核。MCP信号与HID0[EMCP]进行逻辑与运算。为了使MCP有效,HID0[EMCP]和MSR[ME]都必须置高。如果603e核被禁用,内部的MCP自动的从NMI_OUT引脚上输出。在核禁用模式下,NMI_OUT应该连接到主处理器的MCP管脚上。存储控制将MCP有效在下列情况下:

. 校验错误

.ECC双比特错误

.当最大数目单比特错误水平到达的时候ECC单比特错误出现

60X总线数据校验管脚,dp【0:7】,与别的功能复用。他们可以在硬件复位的时候配置为校验管脚。

局部总线有以下专用的校验管脚:

. SIUMCR[PBSE],校验字节选择使能,PGTA/PUPWAIT/PGPL4/PPBS用于字节校验

.SIUMCR[LPBSE],局部总线校验字节选择,如果LPBSE=1,那么将配置LGTA/LUPWAIT/LGPL4/LPBS为局部总线校验字节。

另外TESCR1,TESCR2等寄存器都与校验操作相关。

2 读-调整-写

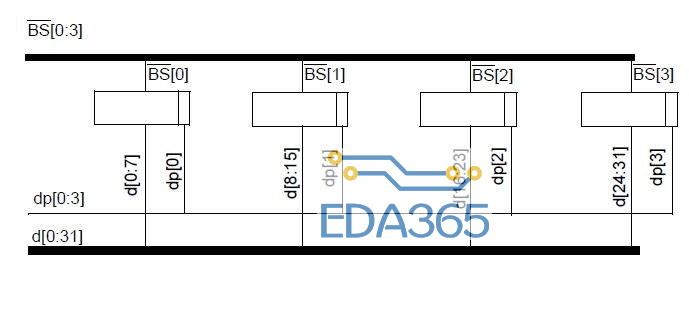

为了支持一般校验,一个称为校验存储器的存储器是必须的。校验存储器有一个额外的与每个字节相关的比特。额外的比特和相应的字节一起输入和读出。图3表示32比特宽度校验存储器。d【0:7】用于控制那个字节别写人。如果一字节写人地址0,BS[0:3]为0x0111.如果只有d【0:7】和dp【0】被写入,而d【8:31】以及dp【1:3】被屏蔽。

低容量会导致校验存储器变得十分的昂贵。如果成本是个考虑因素,那么读-调整-写校验可以派上用场。其目的是为了避免暗光的校验存储器并使用一般的非校验存储器用于数据存储和校验。

注意到,仅有1字节用于校验存储。如果写了1字节到地址0,那么BS[0:7]为0x01111111.如果我们使用PBS作为校验字节选择,PBS和所有的BS逻辑或。如果BS[0]激活,那么相应的PBS【0】也是出于激活状态。在数据总线上,d【0:7】有效当d【8:63】有无效数据的时候因为我们只写了一个字节。相应的校验位dp【1:7】是从无效数据产生的因此它也是无效的。在写的时候,因为bs【1:7】是高电平,无效的d【8:63】并没有写入存储器。但是为了校验,无效的dp【1:7】同dp【0】被一起写人。小于端口宽度的写会破会校验。

由一般校验和一般非校验存储器产生的问题是比较清楚的,比较容易理解为什么一个RMW对于客服问题是必须的。如果BANK被编程为RMW并且写数据小于端口宽度,对于写操作,存储控制器首先做一个端口宽度的读,然后做一个端口宽度的写。以一个1字节写人地址0作为例子,首先PowerQUICCII从地址0,1......7读数据。出现在数据端口的数据为新的写入数据d【0:7】和刚才读入的原始数据d【8:63】组成。因此,所有的数据是有效的而且所有对于d【8:63】的校验数据被计算并且被重新写人校验存储器,避免了校验破坏的问题。对于RMW,结果是使用一般的存储器并且成本是较低的。代价是每次小于端口宽度的写PowerQUICCII都有做一次额外的读操作,增加了总线周期。

3 初始化

以下章节介绍的是ECC和读-调整-写的初始化

3.1 ECC初始化

在使用前ECC存储器必须初始化,这部分讨论发生了什么如果CPU访问非初始化ECC存储bank。上电复位以后,数据和ECC存储器包含‘gabbed’。CPU开始存储有效的数据。一般情况下,宽度是32位或者更小。因为bank是ECC使能的,那么端口的宽度必须是64比特。一个小于64比特的写会自动触发读-调整-写,因为ECC是基于64比特设置的。PowerQUICCII必须回读64比特数据,将心数据和回读数据组合然后产生新的数据,同时计算新的ECC校验。但是在回读的过程中,因为存储器是为初始化的,ECC校验常常是不和数据匹配的,这样会触发以外的ECC错误。初始化ECC存储器而不出现ECC报错,那么设置TESCR1[DMD]以禁止数据报错机制。然后开始初始化ECC存储器空间。初始化以后,清楚DMD位开始正常操作。

3.2 读-调整-写 初始化

像ECC一样,RMW必须在使用前初始化。设置TESCR1[DMD]并初始化整个存储bank。清除TESCR1[DMD]开始一般操作。设置LTESCR1[DMD]进行局部总线的一般操作。

3.3 一般校验

一般校验不需要初始化。

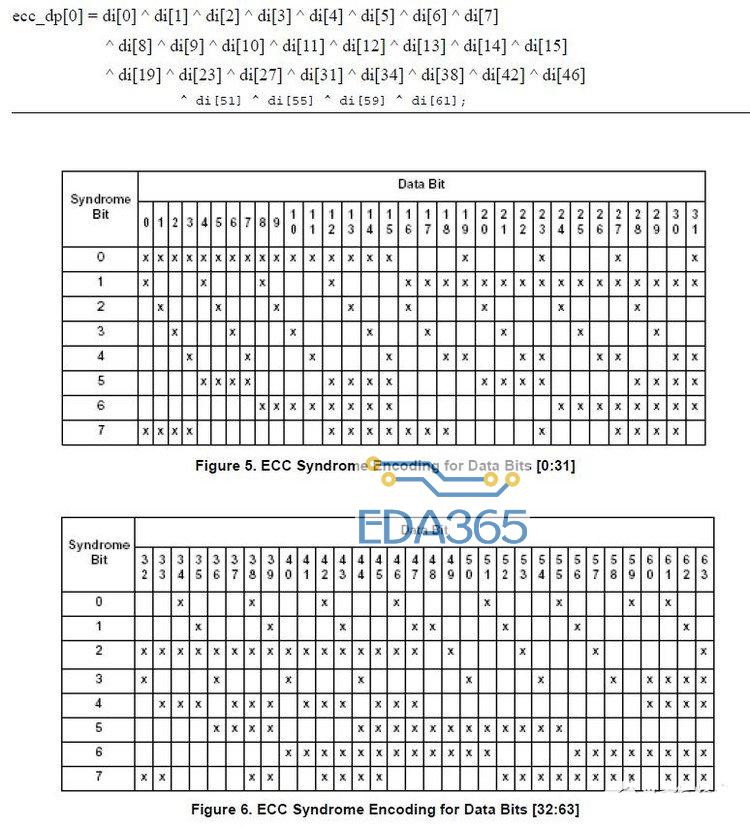

4 ECC 编码

ECC校验比特位等于所有数据为的或运算。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多