上一章大体介绍了存储器的发展历程和其各个类别的特点,那么存储器在整体的系统里是如何工作,如何与cpu起到一个协同作用,这一章节会详细介绍。

存储器的层次按照它的3个指标即速度,容量,每位价格进行划分:

寄存器=>缓存=>主存=>磁盘=>光盘,越是上层的存储器它的容量越小,速度越快,每位价格越高,越是下层的存储器容量越大,速度越慢,每位价格越低。寄存器是CPU中的一个存储器,CPU实际上是拿寄存器中的数进行运算和控制,它的速度最快,价格最高,缓存也被设置到了CPU中。

其中,缓存与主存的作用主要是为了解决CPU与主存速度不匹配的问题,因为CPU速度要快与主存,而缓存也快与主存,只要将CPU近期要使用的数据调入到缓存中,CPU直接从缓存中获取数据,来提升数据的访问速度,降低CPU的负荷。主存与缓存的数据调动是由硬件自己完成的。

主存与辅存主要用来解决存储系统的容量问题,辅存比主存速度低,并且不能被CPU之间访问,但它容量大,当CPU需要运行程序时,将辅存的数据调入到主存,CPU在来访问。主存和辅存之间的数据调动由硬件和操作系统共同完成。

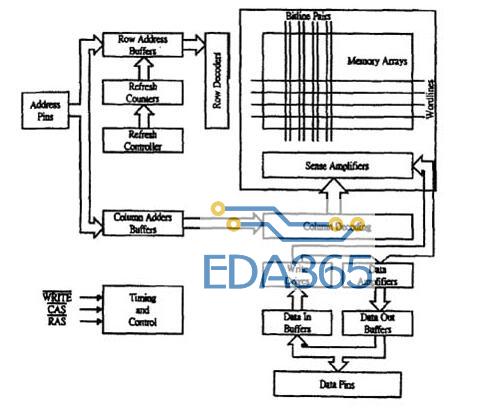

主存储器的功能是能由CPU直接编写程序访问的存储器,它存放需要执行的程序与需要处理的数据,只能临时存放数据,不能长久保存数据。其组成包括:

存储体(MPS):由存储单元组成(每个单元包含若干个储存元件,每个元件可存一位二进制数)且每个单元有一个编号,称为存储单元地址(地址),通常一个存储单元由8个存储元件组成;

地址寄存器(MAR):由若干个触发器组成,用来存放访问寄存器的地址,且地址寄存器长度与寄存器容量相匹配(即容量为1K,长度无2^10=1K);

地址译码器和驱动器

数据寄存器(MDR):数据寄存器由若干个触发器组成,用来存放存储单元中读出的数据,或暂时存放从数据总线来的即将写入存储单元的数据。

主要技术指标:

存储容量:一般指存储体所包含的存储单元数量(N);

存取时间(TA):指存储器从接受命令到读出∕写入数据并稳定在数据寄存器(MDP)输出端;

存储周期(TMC):两次独立的存取操作之间所需的最短时间,通常TMC比TA长;

存取速率:单位时间内主存与外部(如CPU)之间交换信息的总位数;

可靠性:用平均故障间隔时间MTBF来描述,即两次故障之间的平均时间间隔。

高速缓冲存储器(缓存)

高速缓冲存储器的设计理念:为了解决由于I/O设备向主存请求的级别高于CPU向主存请求,也就是说I/O设备在使用主存时,CPU要等待I/O设备访存,导致 CPU工作效率降低,可以在CPU与主存之间加一级缓存,这样CPU可以从缓存中获取数据,另外主存的速度要低于CPU,缓存也是为了解决这俩个硬件设备速度不匹配的问题。

程序访问的局部性:即程序的数据和指令在主存中是连线存放的,并且有些指令和数据往往被多次调用,循环什么的,这样CPU在访问主存时只要将近期需要使用的数据和指令放到Cache中,就可以在一定时间内一直访问Cache,称缓存命中。

缓存的工作原理

将主存和缓存分成若干个块,每个块存储的容量都是相同的,任何时刻都有一些主存的块处在缓存块中,可以将缓存当成主存的一个映射,CPU在读取主存的某个字时都会先去缓存中访问,有二种可能,一是缓存中有当前字,CPU直接访问(CPU与缓存通常一次传送一个字)称为缓存命中;另一种是所需的字不在cache中,此时需要将该字所在的主存整个块一次调入Cache中(缓存与主存是按照字块传送)称为缓存不命中。主存与缓存之间数据的调入是由机器硬件自动完成的,用户编程时使用的只是主存地址,也就是说cache对我们来说是透明的。

我们平时在写程序时所说的缓存指的是主存到辅存(或者说是内存到硬盘之间设立一个类似于缓存的区域)来减少磁盘的IO提升性能,而这里的缓存指的是CPU与主存之间的。

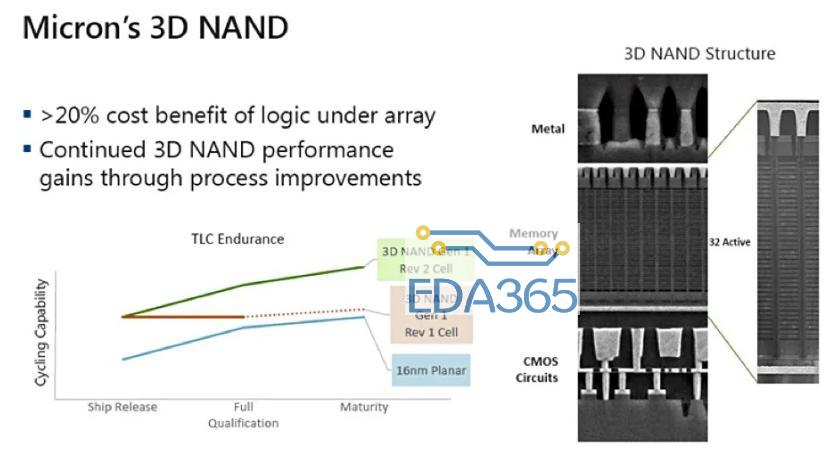

近年来,全球的内存产业在市场需求的影响下得到了充分的发展。从2016年开始,内存的价格持续的高涨,内存俨然已成为大家最关注的半导体器件之一,内存的趋势发展以及供需状况也是大家特别关注的话题。而作为内存产业的核心技术之一,存储控制器在内存产业的发展过程中,其关键性地位更是与日俱增。而闪存芯片拥有着巨大的市场潜力,未来将如何发展?让我们拭目以待。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多