S3C2440A芯片中的时钟控制逻辑可以生成所需的时钟信号,包括用于CPU的FCLK、AHB (Advanced High-performance Bus) 总线外围设备的HCLK,以及APB (Advanced Peripheral Bus)总线外围设备的PCLK。S3C2440A有两个相锁循环(PLLs):一个用于FCLK、HCLK和PCLK,另一个用于USB块(48 Mhz)。时钟控制逻辑可以使用无PLL的慢时钟,并且可以通过软件控制决定将时钟是否连接到外围块,这将减少芯片的功耗。

1 时钟源的选择

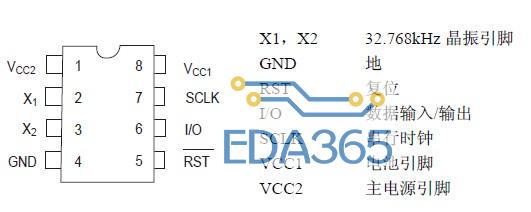

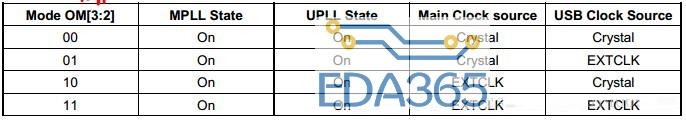

S3C2440A芯片的时钟来源有两个,一个是外部晶振(XTIpll 和 XTOpll),一个来自外部时钟输入(EXTCLK),用哪一个时钟源取决于引脚 OM3和OM2。时钟源选择如下表所示:

表1.1 时钟源选择

图1.1 相关引脚的硬件连接

注:

(1)尽管MPLL在复位之后开始运行,但是MPLL输出(MPLL)不作为系统时钟使用,直到软件将有效的设置写入MPLLCON寄存器。在此有效设置之前,来自外部晶体或EXTCLK源的时钟将直接用作系统时钟。即使用户不想改变MPLLCON寄存器的默认值,用户也应该将相同的值写入MPLLCON寄存器中。

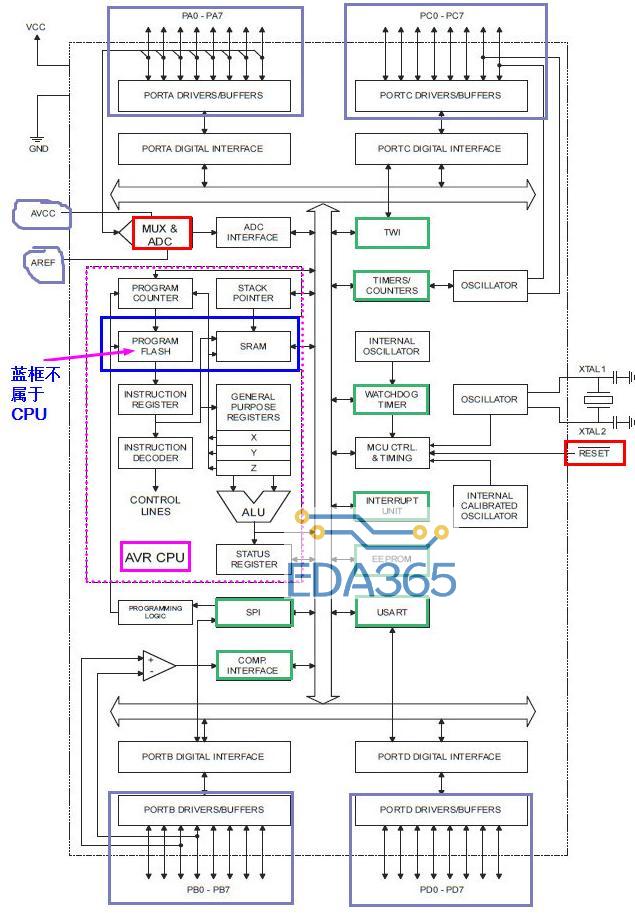

2 系统时钟框图

时钟框图说明:首先,OM[3:2]决定哪的外部时钟源作为系统时钟源,接着MPLLCONL寄存器设置P/M/S,以此得到输出时钟Mpll,CLKCNTL寄存器决定那个内部组件接入时钟,系统上电默认是接入的。 CLKDIVN寄存器决定HCLK和PCLK的频率。

3 上电时,时钟配置时序图(假设外部时钟源已经选择了晶振)

过程解析:

1)上电 ,产生复位信号,等待电源稳定才输出高电平。

2)在复位信号上升沿检查M[2:3]引脚状态,并锁存。

3)在此期间,系统时钟源为外部时钟。

4)PLL适应调整自己的参数,CPU停止工作。

5)调整完毕,系统时钟配置完成。

4 如何配置系统时钟

配置顺序:

1)检查引脚OM3和OM2引脚的状态

2)配置MPLLCON寄存器(0x4C000004),主要是设置M/P/S的值

官方手册给出了一个参考的配置表:(直接按照手册推荐的几个配置来,不然有可能出问题)

3)设置分频比,即配置CLKDIVN寄存器(0x4c000014)

5 实验验证

笔者所使用的开发平台为JZ2440开发板,通过编程在配置时钟源的情况下和不配置时钟源的情况下观察LED灯的闪烁速度,明显可以看到是两种不同的闪烁速度。

部分程序:

/* 设置系统时钟*/

ldr r0 ,=0x4C000004

ldr r1 ,=(92<<12)|(1<<4)|(1<<0) /*设置mPLL=400MHz*/

str r1 ,[r0]

ldr r0 ,=0x4C000014

ldr r1 ,=0x5 /*设置HCLK=100MHz,PCLK=50MHZ*/

str r1 ,[r0]

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多