S3C2440有三种时钟:FCLK(用于CPU核),HCLK(用于主机模块),PCLK(用于外设).两种PLL(锁相环):MPLL(用于设置FCLK,HCLK,PCLK),UPLL(用于设置USB设备),.

S3C2440的CPU核工作电压为1.2V时,主频FCLK可以达到300M,CPU核工作电压为1.3V时,主频FCLK可以达到400M.为了降低电磁干扰,降低板间的布线要求,s3c2410/s3c2440外接的晶振通常很小,一般为12M,那么如何达到主频FCLK的400M的呢?------PLL倍频。

一.设置主频FCLK主要是通过MPLL来软件实现倍频。MPLL主要由3个值MDIV,PDIV,SDIV来决定。而这3个值是由MPLLCON寄存器决定的,MPLLCON的第12位到第19位的值为MDIV,如下所示。

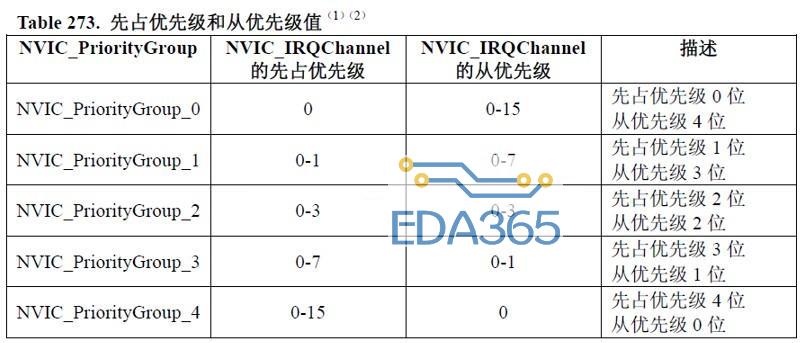

* 对于MPLLCON寄存器,[19:12]为MDIV,[9:4]为PDIV,[1:0]为SDIV |

二.设置好了MPLLCON寄存器也就基本上算是设置好了FCLK,可以在此基础上设置HCLK,PCLK,主要是设置分频比,主要通过设置CLKDIV寄存器设置。

三.代码详解:(参考韦东山大哥代码)

1.设置/启动MPLL

#define S3C2410_MPLL_200MHZ ((0x5c<<12)|(0x04<<4)|(0x00)) |

2.初始化定时器0,并设置中断。

/* |

3.执行make生成timer.bin。烧入Nandflash中后运行,即可看到4个LED每1S闪烁一次。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多