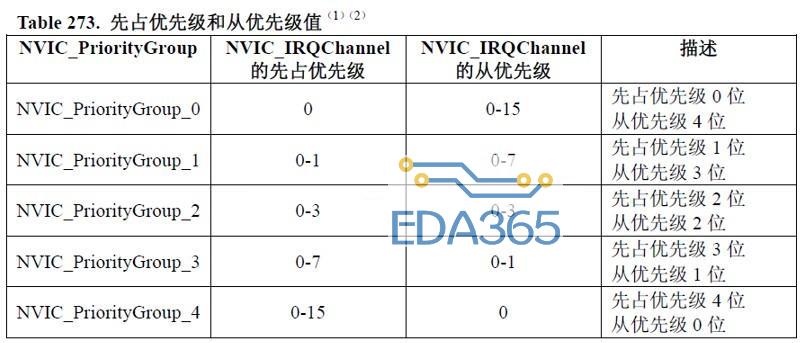

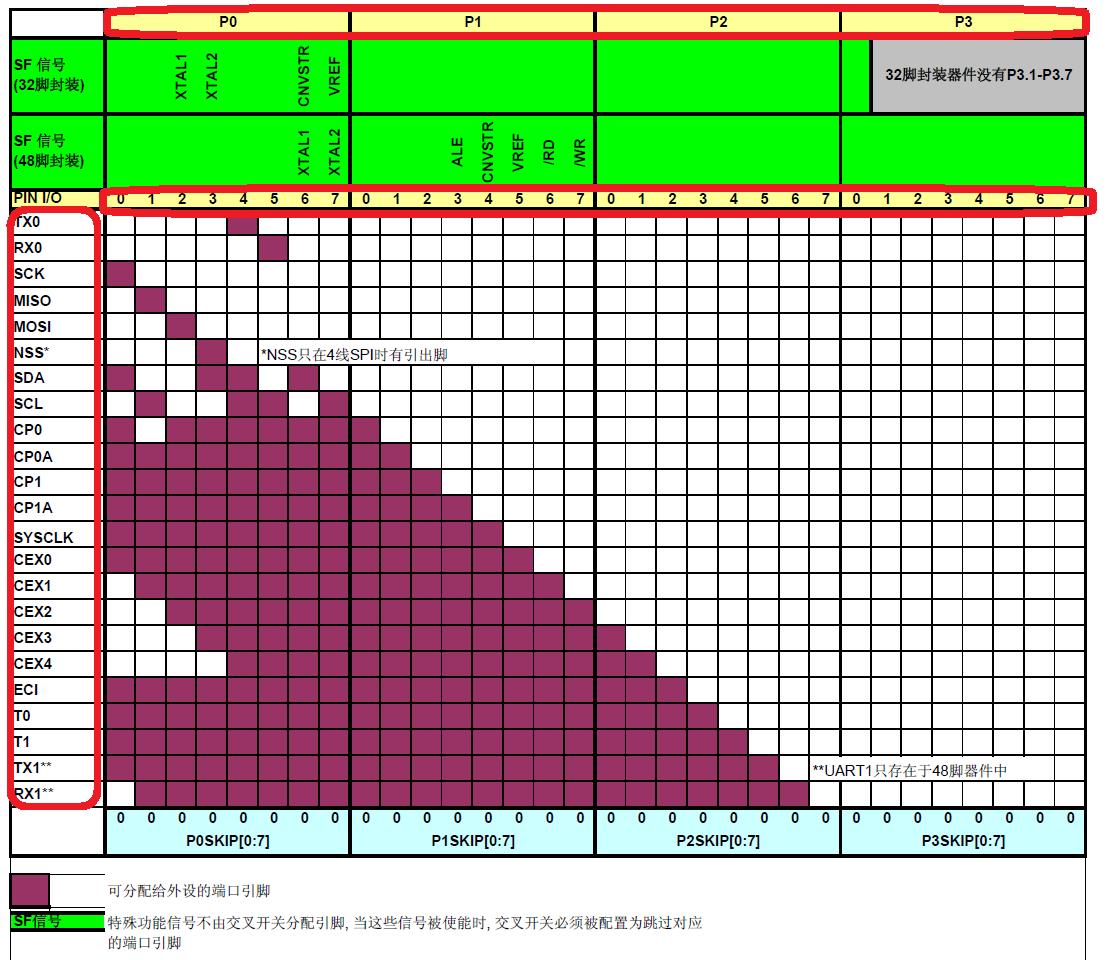

一、背景: 很久前用过C8051,现在有相关需求需要重新使用C8051,然后发现一年前开发的相关经验都忘得 基本上差不多了。连最基本的GPIO口配置还得重新来看手册,所以有此文,做个记录,以备下次快速 开发。 二、正文: 首先是GPIO口的配置步骤: 1. 用端口输入方式寄存器(PnMDIN)选择所有端口引脚的输入方式(模拟或数字)。 2. 用端口输出方式寄存器(PnMDOUT)选择所有端口引脚的输出方式(漏极开路或推挽)。 3. 用端口跳过寄存器(PnSKIP)选择应被交叉开关跳过的那些引脚。 4. 将引脚分配给要使用的外设(XBR0、XBR1、XBR2)。 5. 使能交叉开关(XBARE = 1)。 先着重说明下,什么是"优先交叉开关译码器(Priority Crossbar Decoder)": 这玩意儿的这个名称,我暂时只在Silicon的单片机上见过,也许是因为只有该类型MCU用这种IO 口分配机制吧。我们平时使用的MCU,其IIC,UART,SPI等等这些外设接口已经被厂商配置成某个或者某 几个IO上,若是需要要用这些功能,直接将该引脚配置成相应规定好的第二功能即可,若是该IO口引脚 不得以被使用,还可以使用重映射功能,将该功能映射到厂商规定的第二个备用IO口。但是Slicon却不 然,它提供的MCU原理图上,光光的,什么都没有,也就是说,基本上这些第二功能接口几乎可被配置 在任意一个IO口上。也就是交叉开关会将这些外设功能按照下图外设功能分配优先级,从高到低分配给 不同的外设引脚,外设功能的优先级如下图:

从优先权最高的UART0开始,这个被固定配置在"P0.4","P0.5",接着在"XBR0"内,SPI配置为启用, 且P0SKIP的第"0""1""2""3"位未被选择为跳过,则对应SPI引脚被配置到"P0.0","P0.1","P0.2", "P0.3"上;若是SPI配置为禁用,IIC启用,且P0SKIP的第"0""1"位未被选择为跳过,则IIC的"SDA", "SCL"被配置在"P0.0","P0.1"上。 即若是该引脚已经被配置,或者在端口跳过寄存器中被设置,则交叉开关会跳过这些引脚,然后分 配到接下来空闲的引脚上,该配置选项即对应于GPIO口配置步骤的3、4、5。Uart口的分配是固定的 原因在于下载引导程序内,需要固定此IO口。 说到这,那就一步步详解GPIO口配置步骤吧。 "1"步骤: 决定引脚输入模式,要么是模拟输入,要么是数字输入,数字输入为复位后的默认配置。 寄存器:"PnMDIN","n"为对应的port口: --> "0",配置为模拟输入; --> "1",配置为数字输入。 "2"步骤: 配置引脚输出方式: 寄存器:"PnMDOUT","n"为对应的port口: --> "0",漏极开路;配合外部上拉电阻,通常用来检测输入。 --> "1",推挽输出。 "3"步骤: 对应的引脚是否被交叉开关分配为第二功能: 寄存器:"PnSKIP","n"为对应的port口: --> "0",对应的引脚不被交叉开关跳过; --> "1",对应的引脚被交叉开关跳过。 此步骤注意:若是引脚已被规定了特殊的使用,譬如VREF,XTAL1/2等IO口,或者被配置为 模拟输入的引脚,对应位在该寄存器内必须被配置为"1"。 "4"步骤: 对应外设功能是否被分配到IO口引脚: 寄存器:"XBR0","XBR1"为 --> "0",不需要分配IO口引脚; --> "1",需要分配IO口引脚。 对于给定的XBRn设置,可以使用优先权译码表确定I/O引脚分配;另一种方法是使用 Silicon Labs IDE 软件的配置向导功能来确定基于XBRn寄存器设置的端口I/O引脚分配。 "5"步骤 使能交叉开关,在使能交叉开关未被打开前,外部引脚保持标准端口I/O方式(输入)。 配置完毕后,未被交叉开关选择到的IO口,均可当做通用IO口使用,通过对应的端口数据寄存器 访问端口P3-0,这些寄存器既可以按位寻址也可以按字节寻址。端口P4(仅C8051F340/1/4/5)使用的 SFR只能按字节寻址。向端口写入时,数据被锁存到端口数据寄存器中,以保持引脚上的输出数据值不 变。读端口数据寄存器将总是返回端口输入引脚的逻辑状态,而与XBRn的设置值无关(即使在引脚被 交叉开关分配给其它信号时,端口寄存器总是读其对应的端口I/O引脚)。但在对端口SFR执行下面的 读-修改-写指令(ANL、ORL、XRL、JBC、CPL、INC、DEC、DJNZ)和对端口SFR中的某一位执行MOV、 CLR、SETB期间例外。这些指令读端口寄存器(而不是引脚)的值,修改后再写回端口SFR。 三、参考文献 详细解说开漏输出和推挽输出 http://blog.sina.com.cn/s/blog_14e0394720102vewa.html 至此,记录完毕。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多