中断的工作原理及ARM中中断控制器的工作模式

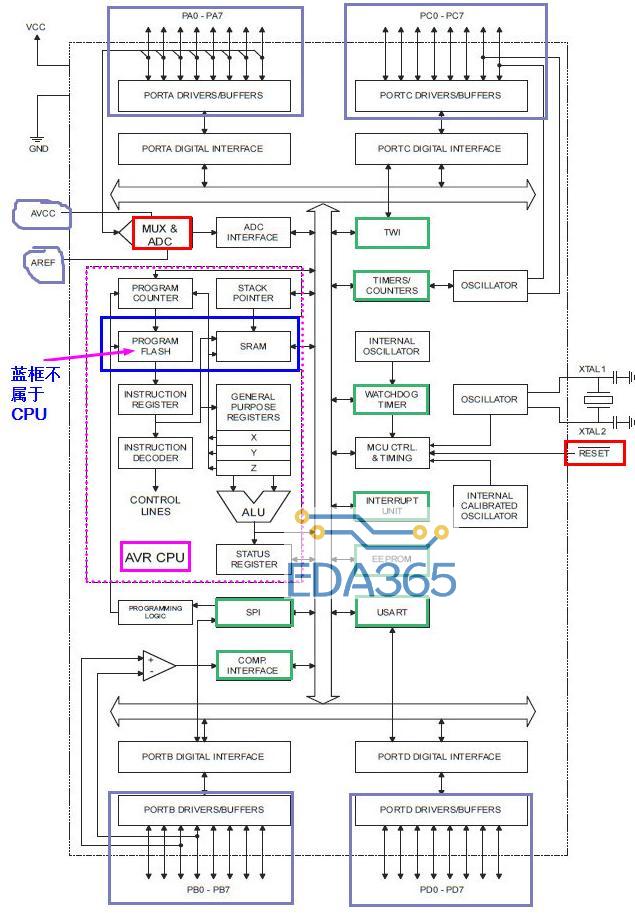

1. 首先介绍ARM内核的中断控制器的几种工作模式:

1.

快中断是为支持数据传输或快速数据通道而设计的,为快速处理快中断。①快中断被设为最高中断优先级;②在快中断模式增设了7个私有工作寄存器,从而避免了由于主工作寄存器数据的保存和恢复而带来了额外开销;③快中断处理程序处于异常向量表的最后位置,因此可紧接异常向量表书写快中断处理程序,而不必进行程序跳转操作,避免了刷新指令流水线和高速缓存。

软件中断是一种由用户设置的同步中断,由程序指令产生,不像硬件中断那样由外部事件触发。软件中断允许运行在用户模式的程序进入监督模式,并运行监督态下的函数。在 ARM7TDMI的硬件调试系统中,应用程序可利用软件中断来申请半自主式操作,例如,打开主机中的一个文件、向调试通道发送一个字符等等(这些操作必须依赖主机中C程序库才能运行,因此被称为半自主式的)。利用软件中断机制,可以直观和高效地仿真调试应用程序。另外,软件中断也可用于一般性的程序控制。

2 .响应中断和中断返回

(1)中断响应过程

1) 保存CPSR到将要执行的异常中断的SPSR;

2)设置CPSR的值:设置CPSR相应位的值使处理器进入特定的处理器模式,按要求屏蔽中断;

3)设置LR寄存器:将中断相应模式的LR寄存器的值设置为异常中断的返回地址;

4)处理程序计数器PC:将PC值设为相应的中断向量的地址。

(2)中断返回过程

1)恢复CPSR:将保存在中断模式中的SPSR值赋给当前的CPSR;

2)将返回地址复制到PC:这样程序将返回到异常中断产生的下一条指令或出现问题的指令处执行。

*中断的响应-返回流程图

系统通常使用一个中断控制器把设备的中断集合在一起,然后再把信号传送到CPU的一个单一的中断管脚。这样可以节省CPU的中断管脚,也给系统设计带来了灵活性。中断控制器有掩码和状态寄存器,用于控制这些中断。设置掩码寄存器中相应的位,可以打开和禁止一个中断,读取状态寄存器可以返回系统中当前活动的中断。

一些系统中的中断可能是硬连接的,例如实时时钟的间隔计时器可能永久地连接到中断控制器的第3管脚。但是,另一些管脚连接什么可能取决于在特定的ISA或者PCI插槽上插入的是什么控制卡。例如,中断控制器的第4管脚可能和第0号PCI插槽相连,某一天该槽上可能插的是一块以太网卡,另一天该槽上可能插的是一块SCSI控制卡。每一个系统都有它自己的中断中转机制,操作系统必须足够灵活才能处理它们。

大多数现代的通用目的微处理器都用相同的方式处理中断。当发生硬件中断时,CPU停止它正在运行的指令,跳到内存中一个位置运行,这里或者就是中断处理代码,或者是一条指令,通过它可以跳到中断处理代码。这种代码通常在CPU的特殊模式(中断模式)下工作,通常,在这种模式下其它中断不能再产生。当然也有例外:一些CPU将中断划分级别,更高级别的中断可以中断低级的中断。这意味着必须非常小心地写第一级的中断处理程序。一般的中断处理程序通常都有自己的堆栈,当它被再次中断而进入另一个中断处理程序之前,用它来存放CPU的执行状态(CPU所有的通用寄存器和上下文)。一些CPU有一组只在中断模式下存在的寄存器,中断处理代码可以使用这些寄存器来存储它需要保存的大部分上下文信息。

关键字:ARM 软件中断  热门文章

更多

热门文章

更多