2007年的DSP可谓“命途多舛”,一向是亲密战友的FPGA突然从外围逻辑应用闯入信号处理系统核心,将DSP功能从高端的FPGA平台扩展到了低成本FPGA,希望能在复杂算法和大量并行处理中补充甚至完全替代DSP。

尽管二者芯片供应商表面上惺惺相惜,但面对20亿美元的新兴高性能信号处理市场,他们的暗战已经开始。

为捍卫自己数十年的主角地位,作为当事人的DSP究竟如何参与竞争?

向多核和SoC发展

与CPU一样,DSP性能很大程度依赖于工艺。摩尔定律表明,工艺的每次提升都可以集成更多的晶体管,从而提升性能、降低成本,还可以降低DSP核电压,实现低功耗。

然而,随着工艺技术进入65nm或者更高级别,提升工艺对于降低功耗的作用已不是那么明显,泄漏电流成了65nm生产工艺中最严重的问题,单一靠提升时钟速度来提升性能的方法已不能满足当今产品对DSP的需求。

“事实上,20世纪90年代初,我们就发现摩尔定律遇到了极限,时钟速度决定性能的关系已经动摇了。所以通过架构创新来弥补——利用工艺实现高集成度,如多核和SoC,” TI首席科学家方进(Gene Frantz)表示。

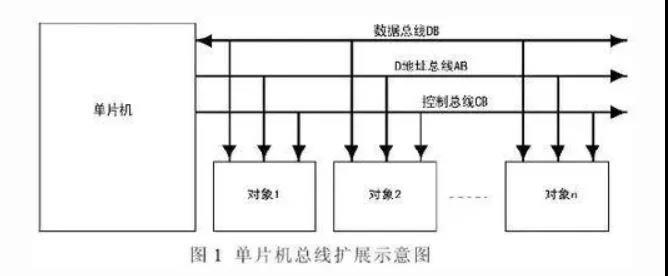

进入到多核和SoC的DSP,表明产业发展进入了一个新阶段——DSP从单独的DSP处理器转变为信号处理系统赋能(enable),DSP只是信号处理系统的一部分,即信号处理已经不再单单是一个处理器,还需要其它硬件和软件。市场需要的不是单纯的DSP处理器,而是解决方案,因此出现了所谓的SoC。DSP成为一个赋能的东西,一个辅助客户进行开发的平台。

同时,由于DSP一般采用哈佛架构,特别适合进行大量数字信号的实时处理。而MCU非常适合于各种控制应用。随着系统需求的增加,在某些应用中,既要求系统具有良好的控制功能,又需要有高速的数据处理能力,因此,融合了DSP和MCU各自优点的混合处理架构无疑是一种良好的解决方案,因此,DSP/MCU融合的架构逐渐受到半导体厂商的青睐,TI、ADI、Microchip等纷纷推出了相关解决方案,力图在这一市场中抢占先机。

不过,方进也坦承,目前多核还存在系统架构和任务划分等挑战,是业界“没有办法的办法”。

低功耗:下一个必争之地

“因为DSP牵扯到高速运算,所以功耗不会降到很低,”提及DSP的低功耗,一个工程师朋友小丁如是说。

然而,近几年来,无论规模大小,处理器的客户都只单纯希望供应商专注于提高器件性能,但差不多从2007年开始,人们的想法发生了变化。开发人员现在首先要面对的问题是“我的设计在功耗方面有一定的限制,德州仪器如何在这方面帮我更多?”方进在提及客户的反馈时说。

自然,处理器的低功耗问题也逐渐浮出水面,并有望成为下一个兵家的必争之地。

定点、浮点DSP

自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案。不过,定点器件至今仍是业界的主流——低成本是主要原因。

最近几年,高密度集成与支持改善使两种DSP在使用方便性与成本上都较为接近。目前,器件类型的选择越来越取决于应用数据集是否要求浮点格式的更多计算功能。因此,设计大规模量产信号处理应用的开发人员现在开始发现浮点格式更多的内在价值。他们将视线投向传统定点DSP开发模式之外的领域,并探索浮点 DSP 所带来的设计机遇。

市场拉动技术

“技术发展有两种情况,一种是技术推动市场(Push),另一种是市场拉动技术(Pull)。只要我们建立了这种关系,了解到来自市场的拉动力,就知道了我们技术和研发上所要推动的。”方进表示。

纵观DSP的发展,第一波DSP应用创新发生在电信领域,目前这个市场仍在稳定增长;第二波为多媒体娱乐产品,目前方兴未艾;而第三波应用创新则可能存在于汽车自动驾驶、人性化医疗保健、数字化安全和绿色环保等领域。

对于应用创新,除了需要性能不断提升的硬件外,更重要的是软件。方进表示:“DSP发展过程中,客户的应用创新主要在软件上,例如智能视频监控中的视频分析。因此我相信信号处理的创新方面,软件还是多于硬件。”

接下来究竟会发生什么?我们只需见证,无需预测。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多