为了提高传输速率和传输距离,计算机行业和通信行业越来越多的采用高速串行总线。在芯片之间、板卡之间、背板和业务板之间实现高速互联。这些高速串行总线的速率从以往USB2.0、LVDS以及FireWire1394的几百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的几个Gbps乃至10Gbps。计算机以及通信行业的PCB客户对差分走线的阻抗控制要求越来越高。这使PCB生产商以及高速PCB设计人员所面临的前所未有的挑战。本文结合PCB行业公认的测试标准IPC-TM-650手册,重点讨论真差分TDR测试方法的原理以及特点。

IPC-TM-650手册以及PCB特征阻抗测试背景

IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。其中PCB板电气特性要求在第2.5节中描述,而其中的2.5.5.7a(IPC-TM-650官方网站下载链接 /zixunimg/rfeefocusimg/www.ipc.org/4.0_Knowledge/4.1_Standards/test/2-5-5-7a.pdf)则全面的介绍了PCB特征阻抗测试方法和对相应的测试仪器要求,重点包括单端走线和差分走线的阻抗测试。

TDR的基本原理及IPC-TM-650对TDR设备的基本要求

1.TDR的基本原理

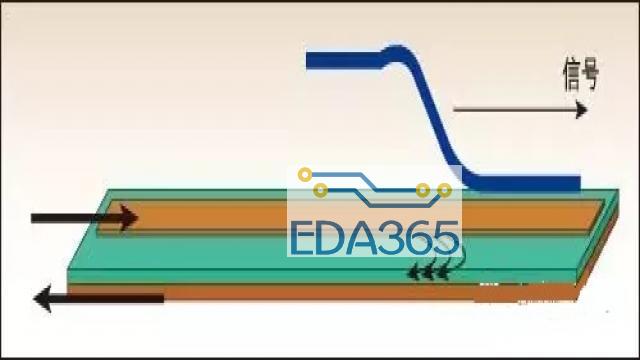

图1是一个阶跃信号在传输线(如PCB的走线)上传输时的示意图。而传输线是通过电介质与GND分隔的,就像无数个微小的电容的并联。电信号到达某个位置时,就会令该位置上的电压产生变化,就像是给电容充电。因此,传输线在此位置上是有对地的电流回路的,因此就有阻抗的存在。但是该阻抗只有阶跃信号自身才能“感觉到”,这就是我们所说的特征阻抗。

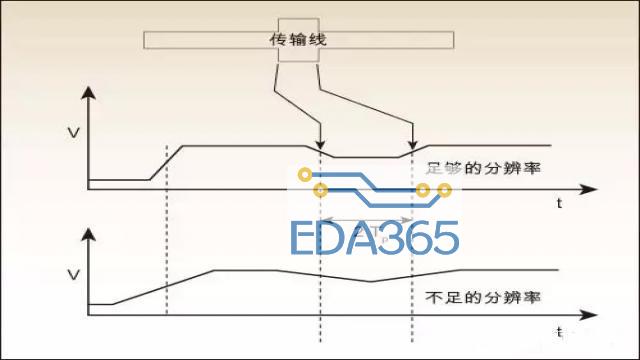

当传输线上出现阻抗不连续的现象时,在阻抗变化的地方阶跃信号就会产生反射的现象,如果将反射信号进行取样并显示在示波器的屏幕上,就会得出如图2所示的波形,从波形中我们可以看出一条被测试的传输线在不同位置上的阻抗变化。

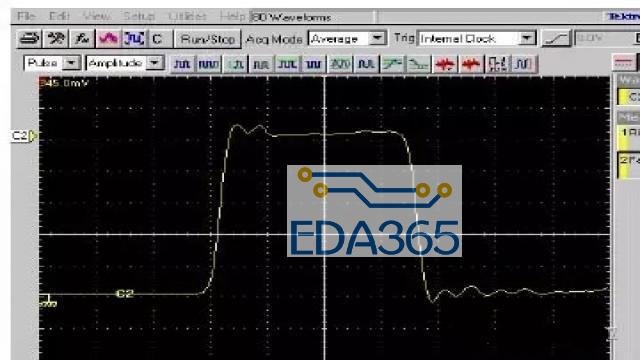

同时我们可以比较图2中的两个波形。这是使用两台分辨率不同的TDR设备在测试同一条传输线时获得的测试结果。对于传输线阻抗变化的反映一个明显而另一个不明显。TDR设备感知传输线阻抗不连续的分辨率取决于TDR设备所发出的阶跃信号上升时间的快慢,上升时间快所获得的分辨率就高。而TDR设备的上升时间往往和测试系统的带宽紧密相关,带宽高的测试系统有更快的上升时间。从另外一个角度来考虑,TDR设备的系统带宽限制了TDR测试的分辨率。在IPC-TM-650测试手册中对TDR设备的上升时间是按照系统上升时间(tsys)来定义的。当我们要测量一台TDR设备的系统上升时间时,我们可以短路一台TDR设备的输出,此时可以测出该TDR设备的(tsys)(上升时间以及下降时间)。例如图3的TDR设备的系统上升时间就高达28ps左右。

图1:阶跃信号在传输线中的传输情况

图2:TDR测试反映传输线的阻抗信息

图3

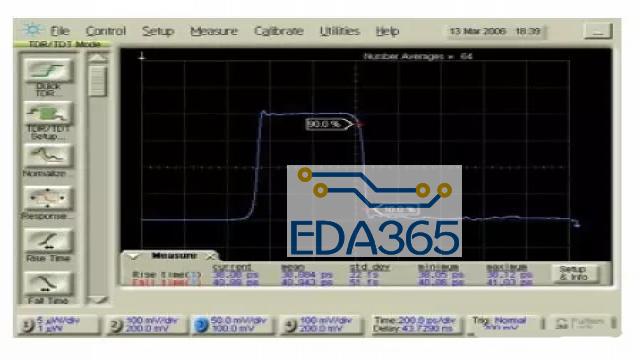

图4:另一台TDR设备的上升/下降时间测量结果

图4是另一台TDR设备的系统上升/下降时间的测试结果,系统的上升/下降时间在38ps~40ps之间。可见不同的TDR设备在系统上升/下降时间上是有很大的区别的,由此带来的就是传输线阻抗测试分辨率的很大不同。

系统上升时间和分辨率的关系可以用下列的公式来描述:

Resolution= (tsys*V)/2,V为电信号在被测试传输线上的传输速率。

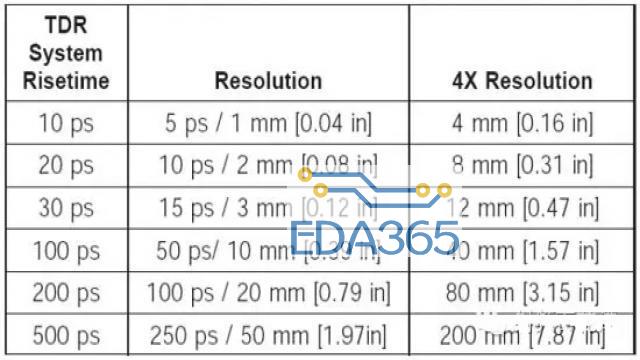

为了方便测试者了解TDR测试的分辨率以及PCB板走线的最小测试长度,在IPC-TM-650测试手册的表4-1(图5)中给出了速查数据。

图5:IPC-TM-650测试手册给出的对照表

IPC-TM-650手册对差分TDR设备的基本要求IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。在以往的IPC-TM-650手册中,对PCB差分TDR测试的要求较为宽松。手册中允许测试者根据TDR测试设备的情况使用两种不同的方法。

方法一:当测试者拥有差分TDR测试设备时,测试设备同时打出两个幅度相等、方向相反的阶跃脉冲,并通过这对差分信号的相互作用直接测出差分走线的阻抗。

方法二:当测试者没有差分TDR测试设备时,测试设备在差分走线(A线与B线)时,先在A线上打出阶跃信号,测试A阶跃信号在A线上的反射特性记作AA,同时测出A阶跃信号在B线上的感应信号,记录为BA。随后,在B线上打出阶跃信号,测试B阶跃信号在B线上的反射特性记作BB,同时测出B阶跃信号在A线上的感应信号,记录为AB。通过对获得的AA、AB、BB、BA四个数值进行计算可以得出差分走线的阻抗。该方法又叫做“Super-Position”。

但是在目前最新版本(2004年3月版)的IPC-TM-650手册中,仅仅保留了方法一中的真差分TDR测试描述。而不再有方法二的“伪差分”TDR测试方法的描述。

两种差分TDR测试方法的对比

方法一:真差分测试法

如图6所示:阶跃信号A和阶跃信号B是一对方向相反、幅度相等且同时发出的差分阶跃信号。

图6:在真差分TDR测试系统上看到的波形

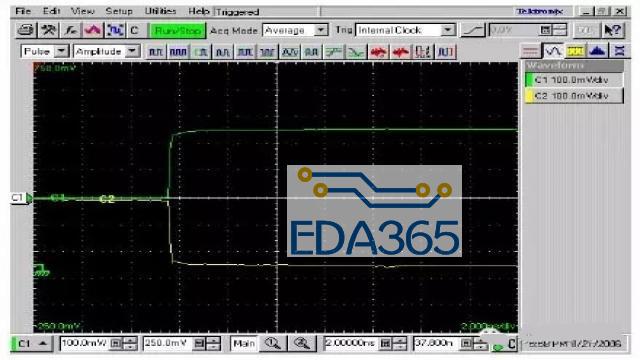

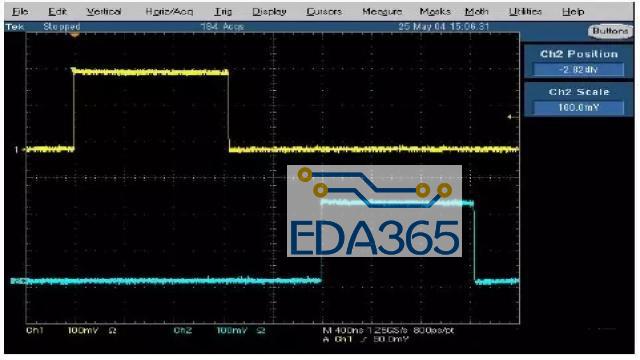

我们不但在差分TDR设备上看到差分的阶跃信号,而且当我们使用一台实时示波器来观测这对阶跃信号时可以证实这是真正的差分信号。

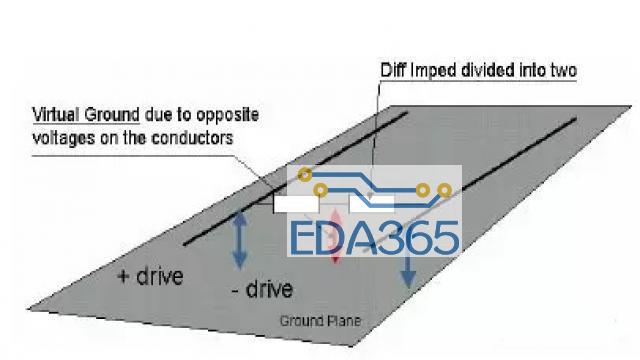

由于注入DUT(被测设备)中的TDR阶跃脉冲是差分信号,因此TDR设备可以直接测出差分走线的特征阻抗。使用差分阶跃信号进行真差分TDR测试,给使用者带来的最大好处就是可以实现虚拟接地,如图7所示。

图7:虚拟地的原理

由于差分走线和差分信号是平衡的,差分信号的中心电压点和地平面是等电势的,因此在使用差分阶跃信号进行差分TDR测试时,只要保证通道A和通道B共地,是不需要与DUT之间接地的。

方法二:“Super-Position”法(伪差分)

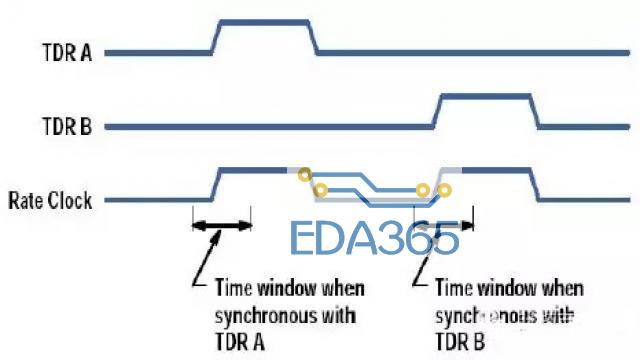

如图8所示,阶跃信号A和阶跃信号B不是同时打出的,且方向不是相反的,因此注入到DUT中的阶跃信号完全不是差分信号。

图8:“Super-Position”法TDR测试原理

在这种“伪差分TDR”设备自身的屏幕上,往往会经过人为的软件调整,令我们看到的阶跃信号同时发出且方向相反的。

但是如果我们用一台实时示波器来观测这两个阶跃脉冲,我们可以看到如图9所示的波形,我们可以看出两个阶跃脉冲之间的真实时序关系,存在着2us的时间差。也就是说这两个阶跃信号不是差分信号。

图9:用实时示波器观察“Super-Position”法TDR系统波形

这样的TDR阶跃脉冲称为伪差分信号,因为它并没有真正实现一个高速差分信号的传输过程,即幅度相等,方向相反。因此这种方法不能直接测出DUT的差分阻抗,只能使用软件计算的方法对差分阻抗测试进行模拟计算。在TDR设备上得到经过计算后得到的2个幅度相等,极性相反阶跃脉冲。这种差分TDR测试带来的局限性是:差分信号之间同时的相互作用无法真实地获得;无法实现虚拟接地,在进行差分TDR测试时通道A和通道B的探头都必须有各自独立的接地点。但是在PCB板内部的真实差分走线附近往往找不到接地点,导致无法在PCB板子内部对真实的差分走线进行测量。

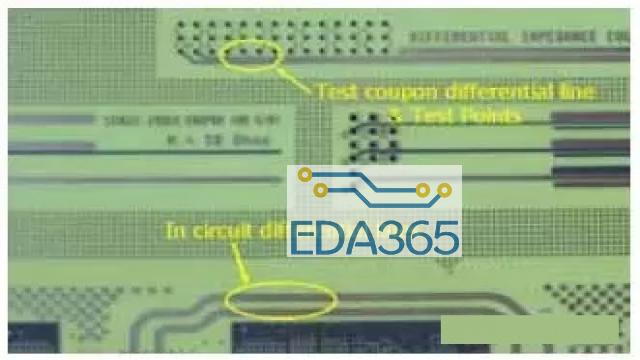

为了解决“伪差分”TDR设备难以实现对PCB板内部真实走线进行差分TDR测量的问题,一般的PCB生产商都会在PCB板的周围做上带有接地点的差分走线测试条,称之为“Coupon”,图10就是一个典型的PCB板,上方是测试用的“Coupon”,下方是板子内部的真实走线。为了方便探头连接,测试点的间距一般做的很大,高达100mil(即2.54mm),已经大大超过了差分走线的间距。同时还在测试点的旁边会放置接地点,间距同样是100mil。

图10:电路板上Coupon与真实走线的差别

“Coupon”测试的局限性与差异

从图10我们可以看到测试“coupon”和板内真实走线之间的差别:

1、虽然走线间距、走线宽度是一致的,但是“coupon”测试点的间距固定为100mil(即最初的双列直插式IC的引脚间距),而板内真实走线的末端(即芯片的引脚)间距是不同的,随着QFP、PLCC、BGA封装的出现,芯片的引脚间距都远小于双列直插式IC封装(即“coupon”测试点的间距)间距。

2、“coupon”走线是理想的直线,而板内真实走线往往是弯曲的、多样的。PCB设计人员和生产人员很容易将“coupon”的走线理想化,但是PCB板上的真实走线则会因为各种各样的因素导致走线不规则化。

3、“coupon”和板内真实走线在整个PCB板上的位置不同。“coupon”都位于PCB板边沿,在PCB板出厂时往往会被生产商去掉。而板内真实走线的位置则是多样的,有的在靠近板子的边沿,有的位于板子的中央。

由于上述几个差异的存在,导致“coupon”的特征阻抗往往与板内真实走线阻抗存在如下的几个差异:

第一,“coupon”测试点间距“coupon”走线的间距不同,会导致测试点与走线之间带来阻抗不连续。而PCB板内的真实差分走线末端(即芯片的引脚)间距往往是与走线间距相等或者非常相近的。由此会带来阻抗测试结果的不同。

第二,弯曲的走线与理想的走线所反映出来的阻抗变化是不一致的。在走线弯曲转折的地方特征阻抗往往是不连续的,而“coupon”的理想化走线则不能反映由于走线弯曲所带来的阻抗不连续现象。

第三,“coupon”与真实的走线在PCB板上的位置不同。目前的PCB板都采用多层走线的设计,在生产时需要经过压制。当PCB板压制时,板子不同的位置所受到的压力不可能做到一致,这样制成的PCB板在不同的位置上介电常数往往不相同,特征阻抗也当然不同。

可见仅仅对PCB板的“coupon”进行TDR测试是不能完全反映PCB板内真实走线的真实特征阻抗的。无论是PCB板的生产商还是高速电路设计者、制造者都希望能对PCB板内的真实高速差分走线直接进行TDR测试,获得最准确的特征阻抗信息。阻碍真实测试的主要原因有以下两个:难以找到差分TDR探头的接地点,高速PCB设计人员不会在设计高速差分走线时在走线的末端(即芯片引脚)附近放置固定间距的接地点;差分走线的末端(即芯片的引脚)间距是多变的,必需要一个间距可调的差分探头来实现探测

真差分TDR测试的优势

我们之前讨论差分TDR测试方法时,我们了解到如果TDR设备发出的阶跃信号是差分信号,就可以实现虚拟接地,即差分TDR探头无需与被测试的PCB板接地。只要测试者手中有一个间距可调的差分TDR探头即可完成测试。

图11是一个带宽高达18GHz的差分TDR探头在进行差分TDR测试时的情况。它的探针间距可以在0.5mm~4.5mm之间连续可调,即使在测试一个比圆珠笔尖还要微小的测试点时仍然可以非常从容地以单手完成操作。

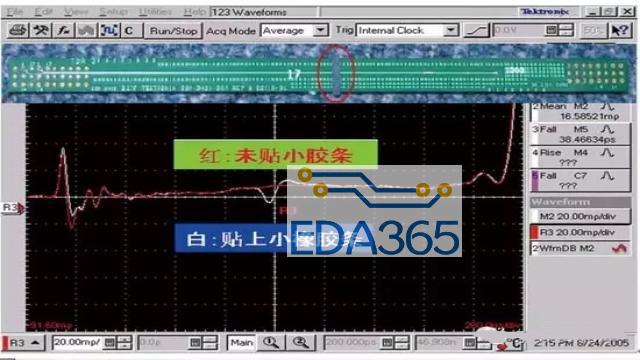

图11:高带宽差分TDR探头进行精密的TDR探测

由于探头的带宽高达18GHz,因此可以获得很高的测试分辨率,图12是对一块“coupon”的差分走线进行测试时获得的结果。红色波形是对“coupon”最初的测试结果,随后在走线上贴上了一个很小的胶条(红色圆圈所示部位)然后再进行测试,获得了如白色波形的测试结果。可见由于贴上小胶条所带来的微小阻抗不连续也能够通过高带宽差分TDR探头清晰地反映出来。

图12:高带宽TDR差分探头进行PCB差分探测所获得的结果

真差分的TDR设备配合高带宽差分探头进行PCB差分特征阻抗测试时,无需在PCB板内苦苦的寻找接地点,只要探针调整到合适的间距,即可轻松的对PCB板内的真实差分走线进行探测。

本文小结:

使用一台真差分的TDR设备,利用差分信号可以实现虚拟接地的便利,配合间距可调的差分TDR探头可以轻松实现对PCB板内真实差分走线的特征阻抗测量。令高速PCB设计人员和PCB制造者在进行PCB测试时获得极高的测试效率和准确的测试结果。

APP下载

APP下载 登录

登录

热门文章

热门文章