摘要:介绍了基于profibus现场总线技术、dsp技术和交流同步采样技术研制的ftu(馈电自动化终端单元)。重点探讨了profibus现场总线技术及交流同步采样技术在系统中的应用及实现。

关键词:馈电自动化终端单元 现场总线 同步采样

电力系统由发电、输电、变电、配电及用电等多个环节组成。配电环节以其不可取代的地位越来越受到人们的关注,如何利用现有的技术来提高配电自动化的水平已成为当前设计人员所关注的重点。

profibus-dp是一种国际性的开放式现场总线标准,专为自动控制系统和设备级分散i/o之间的通信而设计。它性能稳定、传输速度高、价格低廉,具有非常好的应用前景。传统的ftu(feeder terminal unit,即馈电自动化终端单元)的通讯接口大多基于通用异步串口实现,通讯协议多种多样,因此存在着通讯速度慢、协议不规范、不开放等缺点,而现场总线正好可解决此问题。为此,基于profibus现场总线技术、交流同步采样技术和dsp技术等,研制了一种双回线多功能ftu。该ftu除了具有传统的三遥功能外,还具有故障录波、谐波分析、soe(事件顺序记录)、电源品质监测等功能。所有检测数据可通过由spc3协议芯片实现的profibus-dp现场总线接口传送给主站,以满足配电自动化系统的高集成度、智能化、网络化和信息化的要求。1 数据处理算法及同步采样方法

1.1 fft算法的选择与实现

谐波分析的经典方法是傅立叶分析方法。快速傅立叶变换(fft)作为系统的构心算法,其速度直接影响着系统的速度。这里采用是基二时间抽取(dit)fft算法。由于系统的采样值是电压和电流,都为实函数,为提高运算速度,根据fft的奇、偶、虚、实时称特性,把两个通道的采样值组成一个复数数据同时进行计算,从而同时得到两个通道的各次谐波值。这样不仅内存空间节省了一半,而且速度又可提高近1倍。并且对三角函数进行了预先计算,求出了正弦函数在一个周波内n个采样点的值,并存储在一个数组内,而余弦函数的值可由滞后四分之一周期的正弦函数值得到。这样避免了每次对正弦函数和余弦函数的繁琐计算,提高了速度。

1.2 同步采样的实现

由于fft是一种对非周期信号在周期延拓后进行的变换,所以采样点必须均匀分布在一个信号周期内,而且正交样品函数的周期应和信号的周期严格一致,即应当实现严格的同步采样。否则会引起信号的频谱泄漏,带来很大的测量误差,特别是对高频分量,计算出来的值可信度极低。这一点从表1的仿真数据中可清楚地看邮。传统同步采样方法主要分为硬件同步和软件同步两大类。硬件同步方法是用锁相环实时跟踪信号基波频率的变化,实时调整采样频率,实现同步采样。它是一种预防式方法,硬件结构复杂,当信号有较大的畸变或者有强噪声时,误差较大,可靠性不高。软件同步方法是一种初偿式方法,主要采用准同步采样、寻找过零点、加窗插值等步骤对原始采样数据进行重新采样或修正。这种技术虽然在很大程度上能消除频谱泄漏等非步误差的影响,但需要存储容量大,计算复杂费时,难以满足实时系统的要求;而且当信号有较大的畸变或者有强噪声时,寻找过零点亦存在误差问题。为此本文采用一种变采样率同步采样方法,原理如下:

当信号频率与样品函数的频率有偏差时,信号与样品函数的相位会不断改变,如图1所示。图中,实线为信号波形(基波),虚线为样品函数波形。设相邻的两个样位差分别是φ1和φ2,则

δφ=φ2-φ1

δt=tk3·δφ/2π

tk+1=tk+δt

式中,δt为采样周期修正量,tk+1为下一个采样周期。若采样点取为n个,则信号的周期t=n×tk+1,于是可计算出信号的频率为:

f=1/(n×tk+1)

同步采样流程如图2所示。

表1为该方法的仿真数据。数据表明这种方法可以在一到两次修正后快速地跟踪信号的频率变化,达到同步采样的目的。此种方法的优点是硬件结构简单,不需要复杂的锁相或测频电路;同时计算简单快速,存储容量小;而且因为fft具有滤波特性,在信号较大的畸变或者强噪声时,可以克服寻找过零点时的误差问题。这种方法的缺点是每次补偿需要两个周期,且只有存在偏差时才能进行修正,有一定的滞后,当频率变化较大或者变化频率时,会造成一定的误差。但在实际的电网中,电网容量一般较大,频率变化缓慢,若被测电源系统频率变化率为每秒0.125hz,即每秒0.25%,则每两周期的变化只有0.0025/25=0.0001。从仿真数据第10行可看出,基波的设计误差小于0.01%,二次谐波计算误差为0.12%,所以此种同步测量方法完全可以满足实际要求。表1 仿真数据

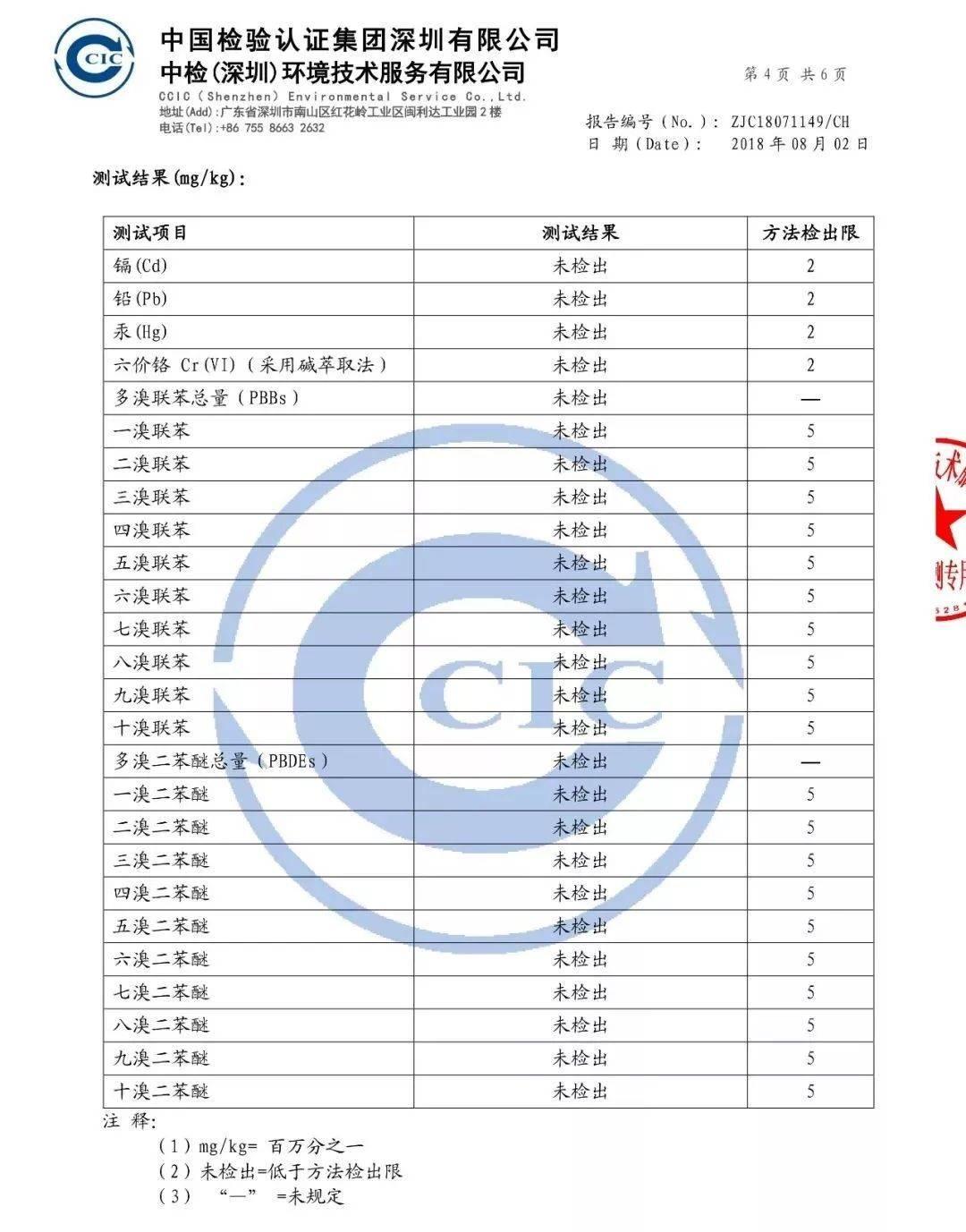

行 号修正次数信号频/率样品函数频率基波计算值(实际值=1000)二次谐波计算值(实际值=100)计算值相对误差(%)计算值相对误差(%)1未修正0.900000944.183475.58142.6734042.67210.9965361000.998960.10104.183064.18320.9999751000.007870.00100.030160.03431.0000001002.904790.00100.000010.005未修正0.9900001000.065430.29111.9551411.96610.999792999.999940.01100.251760.25721.0000001000.312990.00100.000070.008未修正0.9990001000.000610.03101.207631.21910.9999981000.000610.00100.002530.0010未修正0.9999001000.031620.00100.120840.121111.0000001000.000000.0099.999980.001.3 采样次数的确定

在实际电力系统中,信号测量一般取1~19次谐波分量。19位次以上的谐波含量非常小,没有实际应用意义。从信号的保真度来看,采样周期必须满足香农采样定理,即采样角频率ωs≥2ωmax(ωmax是被采样信号的最高角频率),才能避免出现频谱混叠现象。另外,因采用基2-fft算法,所以采样次数必须是2的幂次,这里选择每周期采样64次。当信号的频率为50hz时,采样频率应为50hz×64=3200hz。因系统是两回线系统,a/d变换分两组交替进行,所以系统的采样中断频率应为6400hz。当信号频率偏离50hz时,采样频率跟踪其变化,以保证64次采样正好在一个信号周期内。

2 硬件结构设计

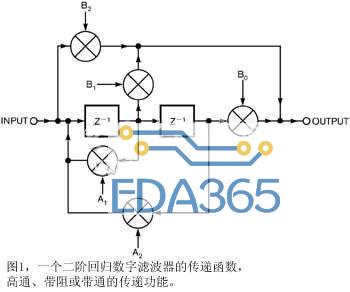

该装置硬件主要由cpu、开关量输入输出通道、频率量输入通道、模拟量输入通道、profibus-dp现场总线通讯接口、实时时钟、电源等部分组成,结构框图见图3。图3 硬件结构框图 现场总线通讯接口由siemens公司的asic协议芯片spc3来实现。spc3集成了profibus-dp的物理层和数据链路层的完整协议,能自动监测波特率,上电后自动维护profibus-dp的从站状态机。片内还集成一个保护监视定时器。如果微处理器有故障,则禁止profibus-dp通道,因而不至于危及外围设备。spc3还有一个公共的中断输出,可通过读取中断寄存器来判断中断源的性质。中断源包括:new-ssa-data、new-prm-data、new-cfg-data、new-gc-command、dx-out等。uart负责将并行数据流转换成串行数据流或将串行数据流转换成并行数据流。

由于对各种电参数的测量和谐波分析不仅需要对交流信号进行高速采样,而且还需要进行大量的实时计算,对cpu的运算速度要求非常高,普通的单片机难以胜任,因此本单元的cpu采用dsp。本次设计采用的dsp是美国ti公司的tms320f206。

三相电源系统每回线需要3路电压通道和3路电流通道,两回线共需12路交流通道。本装置共配置了16路模拟量输入通道,剩下的4路作为直流通道,可作为温度、压力等信号的测量通道。为了测量相角及功率因数,必须同时采样每一回线的6路信号,所以选用两片dallas公司的max125 a/d转换器来完成此项工作。

在电压和电流通道输入端采用了小型pt或ct互感器进行隔离和信号变换,可直接接入220/380v低压信号或100v/5a标准互感器信号来测量高压或大电流系统。既可用3相4线y型接法,也可用3相3线v形接法。在模拟量输入通道前端还配置了二阶有源低通滤波器,以消除高次谐波和噪声信号,减轻谐波分析时出现的频谱混叠现象。

3 软件设计

本装置功能要求复杂,因而软件系统采用了模块化、由顶向下逐步细化的结构设计方法。编程语言主要采用ti公司提供的优化c语言,个别地方采用c2xx汇编语言,提高了软件编程效率和程序的可读性。

软件主要包括主程序、spc3通讯中断服务程序、定时器中断服务程序、a/d变换完成中断服务程序等几个部分。主程序完成硬件初始化、硬件自检、中断任务初始化、谐波分析、电参量计算、越限报警等功能;spc3通讯中断服务程序完成与上位机的通讯、定时器中断服务程序完成各软件定时器的定时、毫秒时钟的维护等;a/d变换完成中断服务程序完成数据的采集、采信通道的切换等。图4为spc3通讯中断服务程序软件流程图。

本文主要从开发的角度探讨了同步采样技术及profibus-dp技术在配电自动化终端的应用,介绍了配电自动化终端的软硬件实现。经实验检验,现场总线接口运行稳定可靠;系统采用的同步采样技术计算快速准确、简单实用,完全满足工程应用的要求。但限于使用的是定点dsp,运算速度相对较慢,所以系统的计算精度和实时性还有待提高。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多