嵌入式系统的发展

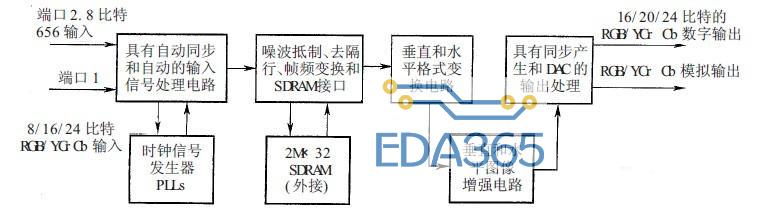

目前,嵌入式系统正在从关键器件为各种类型的嵌入式微处理器、微控制器及其嵌入式DSP、嵌入式存储器等,通过印制板将多个器件组装成的电子系统,向更小的嵌入式系统芯片发展。相应的,嵌入式系统的关键器件则成了SOC系统芯片及其设计SOC所需的各种VC(Virtual Component)模块,包括微处理器VC、微控制器VC与DSP VC,另外还包括各种总线接口模VC、存储器VC、外围电路、RTOS以及专用的处理部件VC(例如MPEG音频与视频译码器等等)。国际上,VC的发展相当迅速,目前VC供应商已经能够提供适合于多条工艺线的、包括MPU、MPEG等在内的各种复杂VC核。

嵌入式系统应用的发展

嵌入式系统应用的发展可从军用与民用两方面来看。就军用来说,20世纪的前沿要属精确制导武器,21世纪的发展可能就是微型化武器。军用嵌入式系统将在实时性、小型化与规模上发展到一个崭新的阶段。就民用来说,嵌入式系统的应用相当广泛,在现代生活中几乎每一个方面都存在嵌入式系统,如移动电话、寻呼机、抢答器、电视机、VCD、CD或DCD播放器,视频游戏控制器、远程控制、传真机、照相机、飞机、轮船、船天器及汽车等等。

今天的芯片技术还不能满足许多嵌入式系统应用的要求,还需要进一步继续向前发展。首先是经济性,对许多应用来说,芯片的价格还是太贵。例如,"蓝牙"技术等。其次是小型化,如心脏启博器,人工视网膜,小型化要求就非常明显了。第三是可靠性,对于常规条件下使用的家电产品等,现在的芯片技术已使产品的可靠性达到了非常令人满意的程度。但对太空,人体等特殊环境下使用的产品的长寿命要求,仍然不是一项容易实现的指标,还有待于芯片技术进一步发展与完善。第四是高速度,许多人工智能应用就是受到了计算速度的限制。第五是智能性,现代的嵌入式系统可以进行逻辑、符号和语言处理等这些被认为是大脑左半球的功能,而且达到了人类自己都感到惊奇的程度,但如何实现与有生命的组织一样灵活而精细的信息处理能力,如发现缺陷,识别和改正错误之类的生物功能等问题,目前尚未找到有效的途径;更不用说各种生命形式中的自律性,自组织,自更新和自发展等最典型的生物功能如何在今后的嵌入式系统中实现了。

嵌入式系统设计的发展

当前的嵌入式系统设计的前沿应当就是嵌入式系统芯片(SOC)。嵌入式系统芯片通常是指集成度大于10万门的至少有一个可编程的VC与存储器VC的芯片。一般说来,系统芯片就要把一个完整的最终产品的主要功能部分集成到一个芯片或一组芯片上。SOC芯片的发展将使印制板(PCB)上的嵌入式系统进一步微型化而成为芯片上的嵌入式系统。系统芯片设计包括嵌入式处理器等许多硬件成份,以及嵌入式OS及应用程序等许多软件成份,这就导致其它的方法,处理与组织的挑战。互连线的延迟,时钟与电源的分布,以及数百万门的布局与布线等,是深亚微米技术物理设计的真正挑战。为了满足SOC设计的挑战,需要采用系统通讯的体系结构以及层次式的可重用设计方法学。也就是SOC的VC的可重用设计问题,以及利用VC构成系统设计的重用问题。

为了使VC具有可重用性,VC的设计是要按下列重用要求完成的。

第一VS的设计是以易于配置的通用性以适合于不同应用为目标的。例如,字节在存储器单元中的存放次序有大端次序与小端次序两种,在处理器VC中就应当具有处理这两种存放次序的能力,以便于与其它VC的配置,形成不同的嵌入式SOC系统。

第二VC的设计是适合于多种工艺技术实现的设计。对于软的VC,其综合脚本文件必须能用许多不同的单元库进行自动综合,并产生高质量的结果;对于硬VC,就要有一个能将VC映射到新工艺上的移植策略。

第三VC的设计应当是一种能用多种模拟器进行模拟的设计。也就是说,最好是Verilog与 VHDL 两种版本的模型与测试台(test bench)都是可用的,而且对所有主要的商业模拟器能工作。VC或测试台只能用一种模拟器工作时是不好移植的。

第四系统芯片中使用的VC应当能独立验证。也就是说,可重用的VC必须具有完全的、独立的测试台与成套验证程序,并提供非常高的检测覆盖。

第五VC的验证是具有高置信度的。也就是说,验证是非常严格的,同时要建立一个实际的原型样机,以用于执行真实程序的实际系统中的测试。

第六要有完备的文档资料,以说明VC的应用与限制,特别是必须建立有效的配置与参数值的文档,清楚地描述配置或参数值的任何限制,以及建立如何使用VC接口要求与限制的文档。

三个重要的国际组织正在通过不同的活动支持面向可重用芯片的设计。1993年成立的ECSI(the European CAD Standardisation Initiative) 主要是通过CAD的标准化努力支持的,1996年成立的VSIA(the Virtual Socket Interface Alliance) 主要是通过开发标准接口支持的;以1997年开始的MEDEA(the Eureka project on Micro-Electronic Development for European Applications)主要是通过技术与应用合作支持的。

利用VC构成系统芯片的设计方法之一就是将硬件与软件协同设计延伸到功能与体系结构的协同设计。功能与体系结构协同设计是从设计产品行为的一个纯功能模型,以适合性能评估的系统体系结构的抽象模型开始的。功能与体系结构协同设计方法学的主要阶段包括功能建模,体系结构建模,功能模型与体系结构模型之间的映射与分析,软件与硬件的实现,以及系统集成。设计的重用是按集成平台实现的。SOC设计的集成平台可有四级:基础的集成平台,IC的集成平台,系统的集成平台,以及制造的集成平台。从RTL-C级的芯片设计到VC集成级的芯片设计的突破要求在体系结构,模型以及设计探索与验证等三个方面有更高级的设计抽象。

为了利用集成平台建立一个派生设计,设计的过程包含四个阶段。首先是建立一个必要的规范,在实现一个派生设计之前,此规模要求大量的系统级模拟。派生设计的技术要求,例如封装,引出头,以及外部电气要求,也必须是定义的。审核由SOC设计用户规范的要求,以及评估通过平台集成处理满足这些要求的可能性的过程,叫做前端接受。其次是在系统设计阶段时,建立体系结构设计并映射到平台的一组VC上。必须将设计映射成一个已有的平台库中的一组已有的VC。将设计映射到所选的VC通常是在体系结构级完成的,这时不区分模块的硬件或软件实现。为了将模块赋与到其合适的VC,模块首先是映到指令模型级的。然后,再映射到行为模型级。第三是硬件与软件设计。硬件设计包括设计安排,功能块设计,以及芯片组装处理。软件设计包括设计并验证软件的组成部分。最后是验证,它是一个贯彻派生设计开发中的过程。

展望未来,明天的嵌入式系统将会比今天的更便宜,更小巧,更可靠,更高效而且更智能化。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多