|

1 引言FIFO(First In First Out)是一种具有先进先出存储功能的部件。在高速数字系统当中通常用作数据缓存。在高速数据采集、传输和实时显示控制领域中.往往需要对大量数据进行快速存储和读取,而这种先进先出的结构特点很好地适应了这些要求,是传统RAM无法达到的。许多系统都需要大容量FIFO作为缓存,但是由于成本和容量限制,常采用多个FIFO芯片级联扩展,这往往导致系统结构复杂,成本高。本文分别针对Hynix公司的两款SRAM和DRAM器件,介绍了使用CPLD进行接口连接和编程控制,来构成低成本、大容量、高速度FIFO的方法。该方法具有通用性,可以方便地移植到与其他RAM器件相连的应用中去[1]。

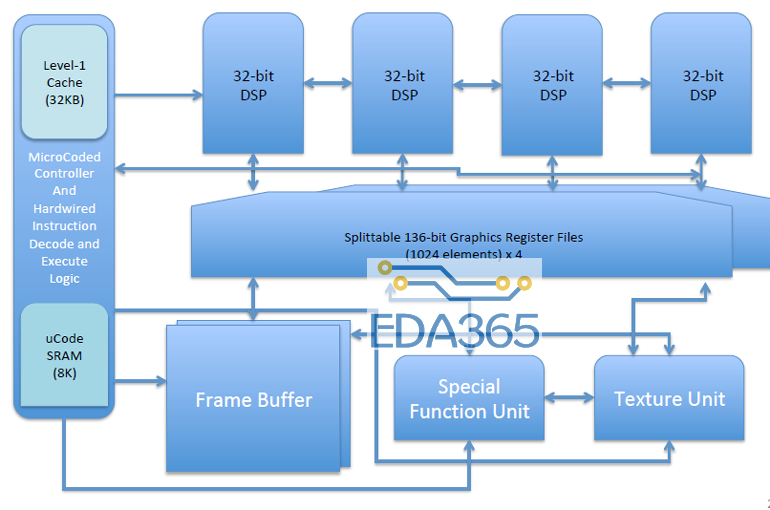

2基于SRAM的设计与实现 2.1 SRAM结构芯片HY64UD16322A静态随机存取存储器SRAM(Static Random Access Memory)是一种非常重要的易失性存储器,它的速度非常快,并且能在快速读取和刷新时保持数据完整性。本系统SRAM器件采用Hynix公司的HY64UD16322A[2]。HY64UD16322A是高速、超低功耗32 Mbit SRAM,内部具有2 097 152个16 bit字容量。采用了CMOS制造工艺、TTL电平接口以及三态输出,具有较大的输入电压和温度范围。同时HY64UD16322A支持DPD(Deep Power Down)模式,保证其在待机模式下功耗进一步降低。 2.2系统硬件设计整个系统采用CPLD作为控制核心器件。CPLD选用Altera公司的MAX7128AETC100-5[3]。MAX7128基于Altera公司第二代MAX乘积项结构,是采用CMOS EEPROM技术制造的EPLD,它集成了2 500个可用门,128个宏单元以及100个I/O引脚。可以看出,HY64UD16322A由地址译码、逻辑控制模块以及大容量存储阵列组成。CPLD接收到FIFO控制信号.按照该SRAM读写时序要求完成相应的读写操作.再通过所构造FIFO的数据输入输出和状态控制接口返回。 | ||||

2.3指针算法程序设计系统采用CPLD作为总控制器件。根据FIFO的特点,需要将SRAM按地址存储用程序控制成先进先出的结构。这里采用指针算法来实现这种结构设计:设置两个指针变量StartPos和EndPos.分别作为进入数据头尾指针。当有新数据写入时,数据从上一次存储最后位置的下一个位置开始存放.存入一个数据.EndPos就自动加1,保持与最后数据位置同步。当EndPos超过整个RAM的最大容量(RAM_SIZE)时,就需要循环返回,从0x000位置存放,一直到EndPos与StartPos重合。这时可以认为RAM已经存满。同理,读出数据时。起始位置StartPos自动加1。当StartPos超过整个RAM的最大容量时,就从0x000位置读取。一直到StartPos与EndPos重合,这时可以认为RAM已经读空。在这两个过程当中,CPLD需要对地址线进行控制.不难发现,写数据的时候Address与EndPos一致,读数据的时候Address与StartPos一致。

3 基于DRAM的设计与实现 3.1 DRAM结构芯片HY57V281620E一般来说。动态随机存取存储器DRAM(Dynamic Random Access Memory)是由大的矩形存储单元阵列与用来对阵列读和写的支持性逻辑电路,以及维持存储数据完整性的刷新电路组成。尽管操作较SRAM复杂,但由于DRAM具有每存储位单元低成本和高密度的优点,使得它们成为商业领域最广泛使用的半导体存储器。本系统的DRAM芯片采用Hynix公司的134 217 728 bit同步DHY57V281620E[4]。它由4块2 097 152x16 bit组成。采用了CMOS制造工艺.LVTTL电平接口。 3.2系统硬件设计同样采用MAX7128AETC100-5完成系统控制。图4是HY57V281620E内部结构以及与CPLD接口的系统连接图。接口控制原理类似2.2所述。不同的是,HY57V281620E内部由行列地址译码、多块大容量存储单元阵列和一些逻辑控制模块组成。

3.4时序控制写入(或读出)数据的时候,CPLD需要模拟FIFO基本的写(或读)操作时序:CPLD接收到nWEN(nREN)和WCLK(RCLK),即当。nWEN(nREN)为低,WCLK(RClK)为上升沿时,将当前I/O上的数据写入(读出)。在数据写入(读出)RAM的时候,CPLD应按照HY57V281620E器件的写(读)时序来控制写(读)操作:CPLD首先控制nRAS从高电平变至低电平,选择行地址。再通过控制nCAS选择列地址。这里,当写入(或读出)数据在同一块当中进行,可以保持nRAS低电平,连续选择多列数据操作(也称作快页模式读写)。当数据地址超过块容量,则需要重新选择行地址,然后再进行连续多列数据读写操作。读写使能控制和SRAM类似,通过nOE和nWE(低有效)来控制。 可以看出,影响所构建FIFO读写速度的主要因素是tPC,这也是决定DRAM速率的关键所在,因此,所构建FIFO的理论速度也应该接近DRAM最高频率。同时,还必须考虑DRAM的刷新操作。这里,系统采用nCAS先于nRAS的方式(CBR),即控制nCS、nCAS、nRAS,并保持nWE为高电平,利用芯片内部计数器决定要被刷新的行。HY57V281620E提供了这种自刷新模式,刷新速率由tREF来决定,通常为64 ms。在系统或某存储块长时间无操作的情况下,需要定时刷新,以保持数据完整。

5 结束语现在,SRAM的数据传输速率可以达到10 ns以内,DRAM要比SRAM稍慢一些。因此。SRAM通常用于高速缓冲存储.而DRAM则通常用来存储较大的数据。从成本来考虑,DRAM比SRAM成本要低得多。采用本文给出的结构和设计思想,避免了以往主CPU接管RAM时的一系列复杂读写操作,而直接类似FIFO使用,接口简单方便,而且避开了传统FIFO器件容量和成本的限制。本文通过理论分析,实际电路设计调试,已成功实现用两种不同结构的RAM构建FIFO,并应用于多个实时高速信号采集系统中。 |

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多