2016年3月22号,北京——Altera,现在是Intel公司旗下的可编程解决方案事业部(PSG),今天发布能够让Stratix® 10 FPGA和SoC支持高达56 Gbps数据速率的收发器技术。Altera今天演示了FPGA业界首次实现的支持双模56-Gbps四电平脉冲振幅调制(PAM-4)以及30-Gbps非归零(NRZ)收发器技术。该收发器技术大幅度提高了一个收发器通道的带宽,使得设备制造商能够灵活的开发未来系统。Stratix 10 FPGA和SoC经过优化,支持数据中心基础设施和电信设备所使用的铜背板和光互联传输极高的数据量。

Stratix 10 FPGA收发器技术将支持1 Gbps至56 Gbps的数据速率。客户可以使用Stratix 10 FPGA来开发支持50G、100G、200G、400G和太比特应用的下一代通信和网络基础设施。收发器的双模功能为客户开辟了开发下一代高端系统的途径,并支持主流和已有背板、铜缆、芯片至芯片和芯片至模组互联和接口,从而保护了客户的投入。Altera一直是IEEE 802.3以太网和光互联论坛(OIF)业界公认的50G-56G PAM-4标准的领导者和贡献者。

Intel公司可编程解决方案集团高端产品营销总监Jordon Inkeles评论说:“数据中心和网络基础设施对带宽需求的爆炸式增长要求我们FPGA所具有的性能和密度能够高速、高效的传送更多的数据。系统要求的数据速率已经超过了28 Gbps,数据传输传统的NRZ调制方法很难满足这种要求。在我们的Stratix 10 FPGA和SoC中实现双模56-Gbps PAM-4和30-Gbps NRZ收发器将有助于客户满足最严格的数据吞吐量需求。”

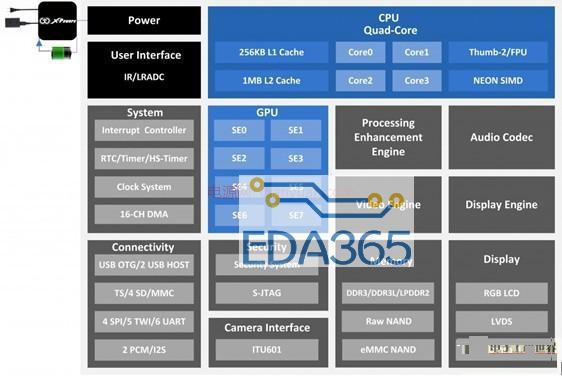

Stratix 10 FPGA使用异构系统级封装(SiP)方法来集成收发器,收发器块和单片FPGA内核架构被Intel的嵌入式多管芯互联桥接(EMIB)技术连接在一起,这样,Stratix 10 FPGA和SoC能够迅速满足所有市场领域日益增长的系统带宽需求;并且收发器块这种方法进一步提高了灵活性和可扩展能力,促使产品尽快面市。

供货信息

将于2016年第四季度开始发售首批Stratix 10 FPGA。Altera在OFC 2016上演示了Stratix 10 FPGA收发器技术。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多