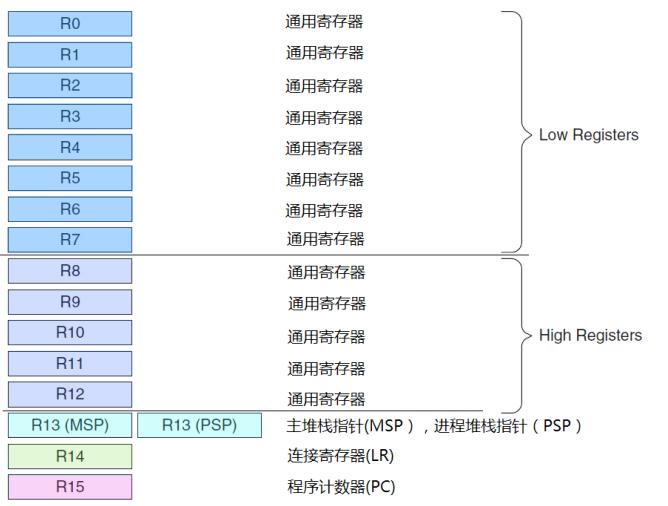

Cortex ‐ M3处理器拥有 R0‐R15 的寄存器组。其中 R13 作为堆栈指针 SP 。SP 有两个,但在同一时刻只能有一个可以看到,这也就是所谓的“banked ”寄存器。

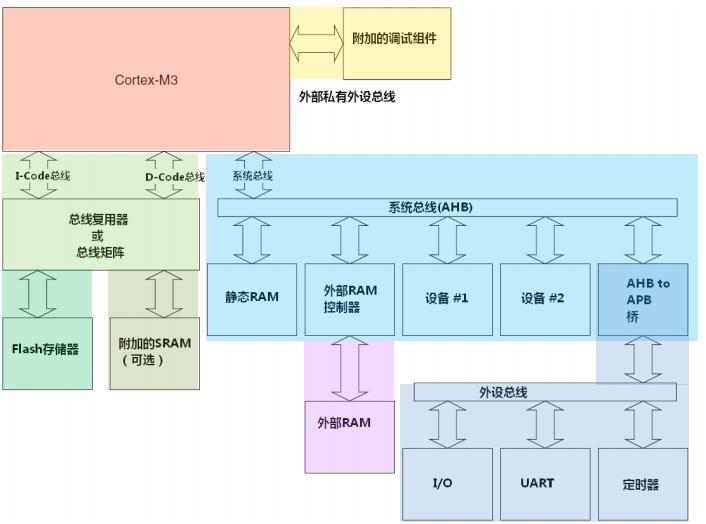

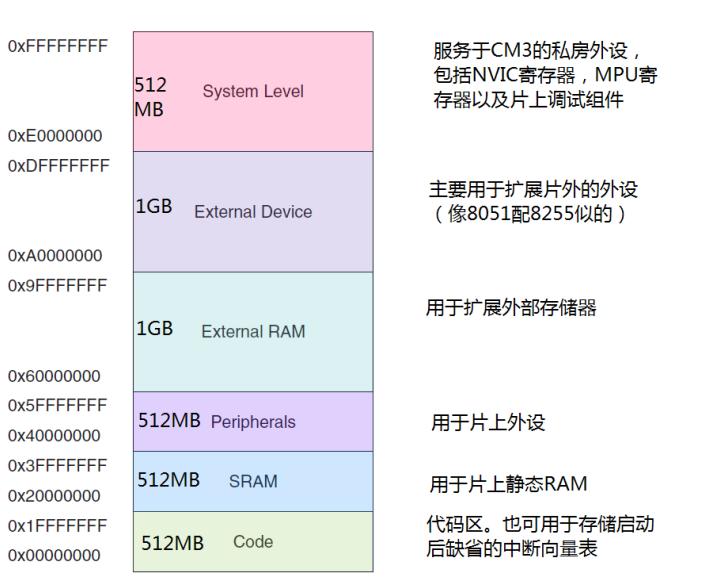

不像其它的 ARM 架构,它们的存储器映射由半导体厂家说了算,Cortex ‐ M3预先定义好了“粗线条的”存储器映射。通过把片上外设的寄存器映射到外设区,就可以简单地以访问内存的方式来访问这些外设的寄存器,从而控制外设的工作。结果,片上外设可以使用 C 语言来操作。这种预定义的映射关系,也使得对访问速度可以做高度的优化,而且对于片上系统的设计而言更易集成(还有一个重要的,不用每学一种不同的单片机就要熟悉一种新的存储器映射——译注)。

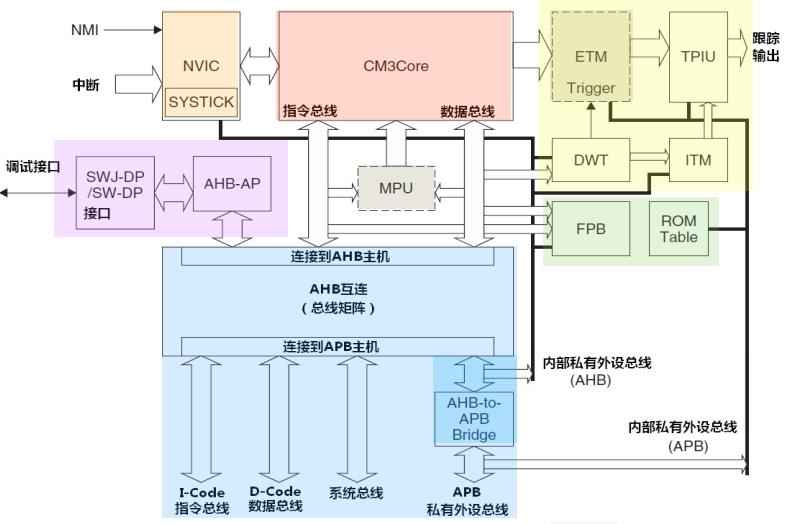

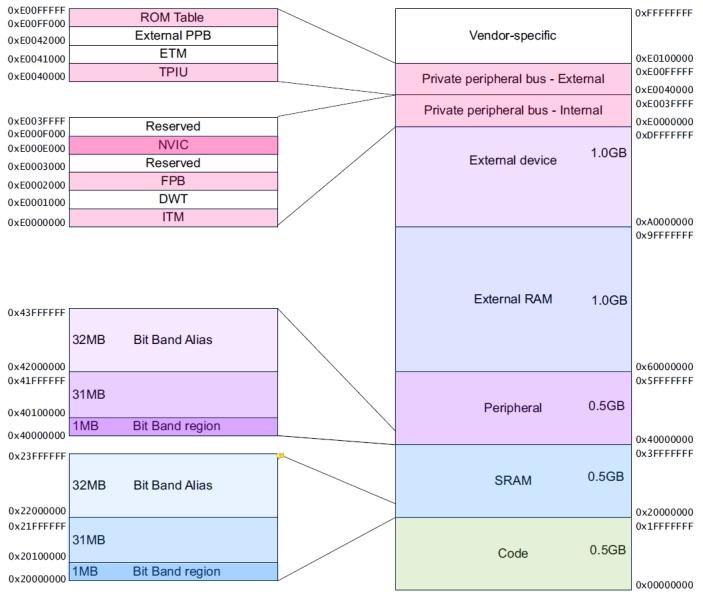

Cortex ‐ M3 的内部拥有一个总线基础设施,专用于优化对这种存储器结构的使用。在此之上,CM3 甚至还允许这些区域之间“越权使用”。比如说,数据存储器也可以被放到代码区,而且代码也能够在外部RAM 区中执行(但是会变慢不少——译注)。处于最高地址的系统级存储区,是CM3 用于藏“私房钱”的——包括中断控制器、MPU以及各种调试组件。所有这些设备均使用固定的地址。通过把基础设施的地址定死,就至少在内核水平上,为应用程序的移植扫清了障碍。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多