美国莱迪思半导体硅解决方案营销总监Shakeel Peera (点击放大)

美国莱迪思半导体(Lattice Semiconductor)于2011年11月28日(当地时间)发布了成本和功耗都比较低的中端FPGA新产品“ECP4”系列。特点是与上一代产品“ECP3”一样,也利用65nm工艺技术制造。制造中端FPGA时,与利用最尖端的28nm工艺相比,利用已成熟的65nm工艺“在今后3~5年里能降低晶圆成本”(该公司硅解决方案营销总监Shakeel Peera)。

“ECP4”系列的主要用途是“最后一英里(Last Mile)的网络设备”(Shakeel Peera)。除无线及有线通信设备外,还能用于各种图像处理装置、安全设备、监视装置及存储器等。

ECP4可以使用的查找表(LUT)数量比ECP3增加约66%,达到了25万个。工作速度也提高了30%。最多可利用16条通道的SerDes电路方面,ECP3支持3.2Gbit/秒的数据传输速度,而ECP4支持6Gbit/秒的数据传输速度。以6Gbit/秒工作时,每条通道的功耗为175mW。

ECP4的嵌入内存容量比ECP3增加了约42%。DSP引擎通过采用DDR寄存器和强化乘法器等,将乘加运算性能最大提高到了ECP3的7倍。通信引擎通过采用硬件IP将功耗降低了约90%。另外,配备了1066Mbit/秒的DDR3内存接口。

为降低成本,不仅采用了富士通半导体提供的成熟度高的65nm工艺,还采用了廉价的引线键合封装。通过采用自主技术,“全球首次通过引线键合支持6Gbit/秒的SerDes”(该公司)。

不过,能以引线键合实现6Gbit/秒的数据传输速度是在通信距离在8英寸以内的芯片间通信时,该公司针对更长的通信距离,准备了倒装芯片封装。

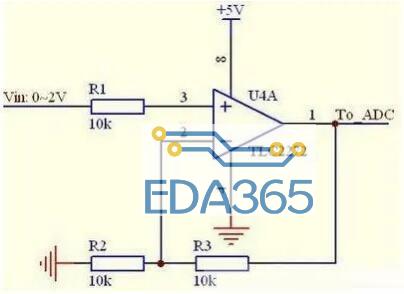

通过采用65nm工艺和引线键合封装,降低了成本。(点击放大)

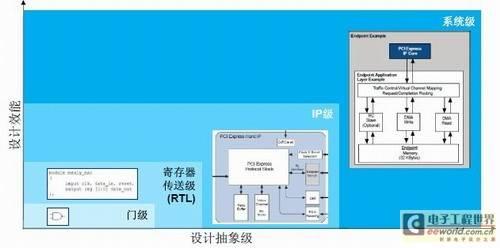

目标市场主要是网络的最后一英里部分。(点击放大)

功耗比28nm工艺低(纵轴为动态功耗+静态功耗)。(点击放大)

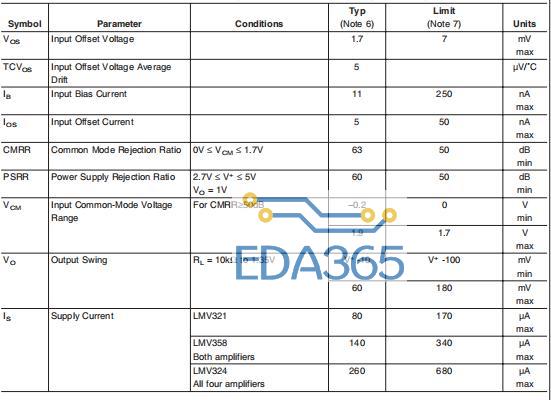

详细数据。(点击放大)

另外,该公司计划继ECP4之后推出的“ECP5”采用28nm工艺(参阅本站报道)。

设计工具“Diamond 1.4”的beta版已经问世,ECP4的工程样品将于2012年上半年提供,支持正式订货的量产品将于2012年下半年提供。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多