开场白:

希望通过这篇文章记录一下自己在调试NAND flash的经验。希望对大家有用。

上个月搞了一块开发板QT210。说实话没有找到很多的datasheet就开始搞了。最早还是从boot说起,说到这这里不得不提到boot中打印的错误信息 ****CRC Error*****。最后还是决定静心调试看看怎么回事。结果发现资料还是确少,怎么办?找了以前的omap开发板。(个人觉得omap的板子 BSP还是做的比较好的)。在omap上调试了一下并测试了一些基本的NAND的读写操作。

210的板子准备在linux中使用MTD去管理者块flash。并且留下了疑问:s5pc110的片子memory map给nand 和 onenand留下了256MB的空间,但是210的板子使用的是三星的1GMB的flash。多余的7百多兆的flash的空间如何管理?

nand bsp分析:

型号:MT29F2G16xxxx

硬件平台:omap3530

在分析之前,确定硬件平台和device的型号还是很有必要的。应为在3530的板子上是使用的LPDDR(micron)。在以前的工作中和供应商打过交道。其实flash的型号以及位宽和一些其他的参数可以从芯片的命名的法则上了解。在查阅了相关文档后确定NAND的型号。

基本的read函数。

下来了解一下nand的操作时序:

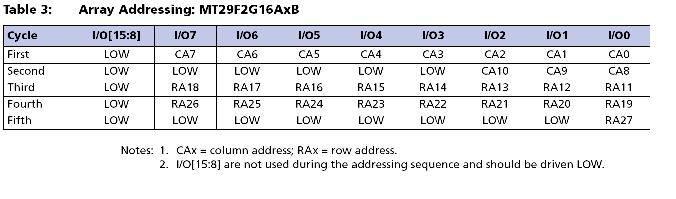

io是复用的。即是data又是cmd。但是注意16bits位宽的device在cmd和寻址时候是8bits位宽,数据读出时候是16bits位宽。

简单通过一个函数:read,但是在read之前先要把上图中现实的cmd 以及addr作用到总线上。这就是软件的作用了。在这里不得不提一下omap的GPMC。其实这就是一个包含NAND Controller的硬件模块。具体的初始化和寄存器设置工作状态在别的文章中解释。(GPMC的设置也是要花时间去调试和跟踪的,不想影响了NAND的分析)

只要记住软件正确的操作了GPMC相关的NAND控制器,就是对NAND devide进行相关操作了。

1,static int NanD_Command(unsigned char command)

2,static int NanD_Address(unsigned int numbytes, unsigned long ofs)

一个是写指令,一个是写地址。

为了方便,没有把代码全部贴上来,逻辑应该是:

(1)NanD_Command(00)

(2)NanD_Address(address)

(3)NanD_Command(30)

(4)read ioregister

这里遇到了两个问题:

第一:read后的数据和nand dump的数据不符合。

第二:如何确定address在device中的具体位置。

先来看看第一个问题。

在read函数后发现buf中的内容不是确定block中page的内容,很是怀疑。后来把buf的具体位置print一下,发现:buf++,但是地址是由小到大的。

buf_start -> 0x8000 0000

....

....

buf_end -> 0x8030 0000

所以要打印block中的内容必须 buf_end - offset。

再来看看第二个问题。

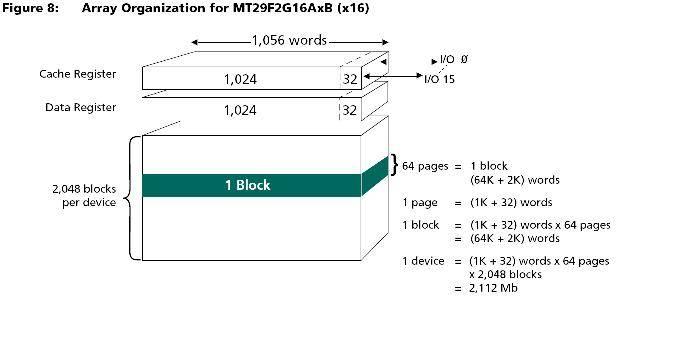

看到这张图其实很熟悉了,只要是看了结构。但是光有这张图还是不够的。

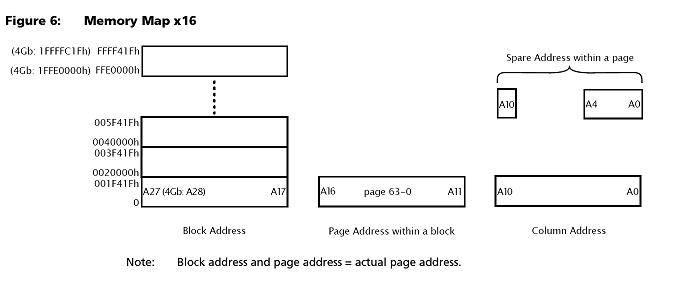

这下知道了为什么分为5个步长的address。其实这和NAND的内部寻址逻辑有关系。

A0 - A10 代表了一个page中的偏移。应为加上32B的oob已经是大于1024words了那么就要使用11个bits来索引。其实在这里面11bit不会全部使用。因为只要1024+32 = 1056words就够了。

A11 - A16 代表了page offset。一共有64page。具体在block中哪一个page使用这6bits来定位。

A17 - A27 代表了block的个数。一共有2048block。这10bit来索引。

下面关键的来了,看看使用的物理地址如何转化到NAND的具体的block的page的col上面。

在linux机器上抄写了一个应用的函数分析一下这些地址。函数如下:

/* NanD_Address: Set the current address for the flash chip */

static int NanD_Address(unsigned int numbytes, unsigned long ofs)

{

uchar u;

NAND_CTL_SETALE(NAND_ADDR) //设置地址锁存

if (numbytes == ADDR_COLUMN || numbytes == ADDR_COLUMN_PAGE || numbytes == ADDR_OOB)

{

ushort col = ofs;

u = col & 0xff;

printf("1st addr %X\n",u);

WRITE_NAND_ADDRESS(u, NAND_ADDR); //第一个address的偏移 因为 io 地址线的低8位有效。

u = (col >> 8) & 0x07;

if (numbytes == ADDR_OOB)

u = u | ((bus_width == 16) ? (1 << 2) : (1 << 3));

printf("2st addr %X\n",u);

WRITE_NAND_ADDRESS(u, NAND_ADDR);

}

if (numbytes == ADDR_PAGE || numbytes == ADDR_COLUMN_PAGE || numbytes == ADDR_OOB)

{

u = (ofs >> 11) & 0xff;

printf("3st addr %X\n",u);

WRITE_NAND_ADDRESS(u, NAND_ADDR);

u = (ofs >> 19) & 0xff;

printf("4st addr %X\n",u);

WRITE_NAND_ADDRESS(u, NAND_ADDR);

/* One more address cycle for devices > 128MiB */

if (chipsize > (128 << 20)) {

u = (ofs >> 27) & 0xff;

printf("5st addr %X\n",u);

WRITE_NAND_ADDRESS(u, NAND_ADDR);

}

}

NAND_CTL_CLRALE(NAND_ADDR); //地址锁存

NAND_WAIT_READY();

return 0;

}

以上函数一些大写的函数做一下说明,就是往NAND Controller (寄存器)中写入指令或是地址。这些源码可以在我的资源中下载。(希望不会有什么麻烦)

还是回到函数本身,看看到底是如何确定地址的。在函数中,写寄存器的代码之前添加了打印,其实可以ubuntu上调试,就是把相关的寄存器操作代码去掉。

第一栏 第二栏 第三栏

假设想要读取0block0page0offset的地址:00000000000 000000 00000000000

假设想要读取0block1page0offset的地址:00000000000 000001 00000000000

假设想要读取0block2page0offset的地址:00000000000 000010 00000000000

假设想要读取1block0page0offset的地址:00000000001 000000 00000000000

假设想要读取1block1page0offset的地址:00000000001 000001 00000000000

假设想要读取1block2page0offset的地址:00000000001 000010 00000000000

注释:

1,第一栏 为 block offset

第二栏 为 page offset

第三栏 为 col offset (可以查阅相关的文章,为什么在page中的偏移叫做或者称为col,是由于flash的发展而来)

2,以上转换过程中BLOCK OFFSET为:0x20000 (一个block的大小是64k words)128kB

3,以上转换过程中PAGE OFFSET为 :0x800 (一个page的大小是1024 words)2048kB

4,顾第二个block的block偏移为 :00000000001

5,由此归纳出一般的线性地址到NAND device的地址转换格式为:

8bit IO 访问

1st cccc cccc

2st XXXX Xccc

3st bbpp pppp

4st bbbb bbbb

5st XXXX XXXb

上述表达式中: c代表col b代表block p代表pageoffset

基本的write函数。

6,在这里再提一个经验,在page offset中read的buf指针是有记忆的,当你预读取在data cache中的时候。其实已经把page offset作用到了NAND片内。顾在read周期性的拉低ALE的同事会从指定的地址读出数据。

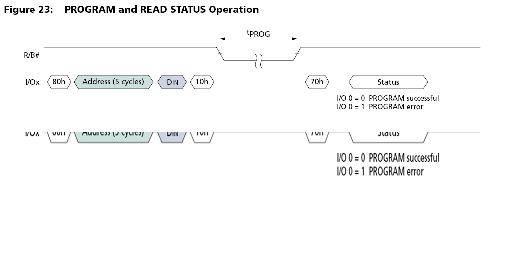

NAND的write操作硬件时序图如下:

查看函数要区分: write在nand的操作中叫做program。(估计是应为在写nand的时候要erase,所以这里叫这种写入方式为 program 个人理解,可能不科学)。

在这里很可惜x-load的代码没有write操作。起原因最小化的代码初始化真个芯片。在这里不得不提一下,在ARM s5pc110的TRM中写的很清楚,片内的rom code初始化了PLL,bus等模块,但是omap3530的片子没有找到相关文档。看了x-load。其中有代码是初始化ARM core的PLL。

在omap中的PLL时钟初始化,如果不是有硬件来完成基本的初始化(锁相),不知道这样的设计是否合理。我总觉的上电后第一条指令,指的是PC取值后的action。在这之前还有很多是硬件模块自己的逻辑完成。不知道这样的理解是否正确。希望 高手 大侠 看了这篇文章后,特别是这段内容,不要吝惜文笔,给予指点。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多