SOPC可编程片上系统是一种独特的嵌入式微处理系统。首先,它是SoC,即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,以FPGA为硬件基础,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件系统在线可编程的能力。

本系统采用了Altera公司的CycloneIIFPGA开发平台和相应的开发工具QuartusII进行系统硬件部分的开发;利用NiosIIIDE实现了语音识别算法的编译、链接、调试和运行;同时还应用了Altera公司独具特色的C2H加速工具,实现了语音算法程序的硬件加速,使系统性能得到了明显的提升。

此次设计采用了二维条形码进行语音特征的存储,一方面是考虑到二维条形码的成本很低,市场应用潜力巨大;另一方面,正因为在个人证件上拥有了二维条形码,系统可以脱离数据库的支持,变得更加灵活实用。

系统结构

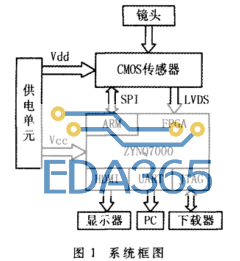

本设计采用SOPC的可编程设计思想,以CycloneII中实现的NiosII处理器为核心,系统架构如图1所示。

图1系统结构框图

中心处理模块可以接收其他模块的数据,并进行处理,再将处理结果送到外部设备进行显示和报告。语音采集模块在用户注册和认证时采集用户口令(即语音),其中包含A/D采样、量化、编码等,并会将数字形式的数据送到中心处理模块等待处理。系统以串口扫描枪做为条码扫描设备,用于读取个人证件上嵌入声纹特征的二维条形码中的数据,这些数据是在用户注册时生成的。

本设计将SOPC设计与二维条形码数据存储相结合,不仅发挥了各自的特点,而且扩宽了应用领域。

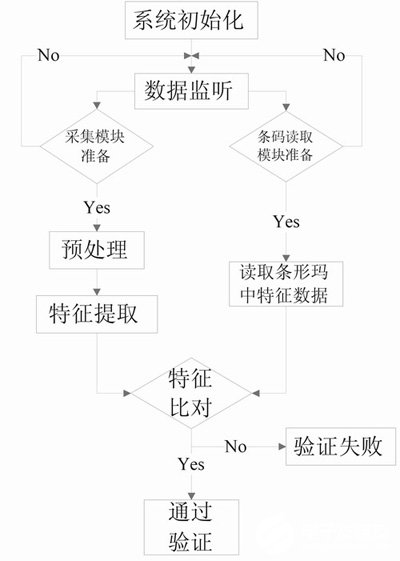

系统工作流程分为注册和验证两个阶段。注册过程需要采集同一用户的多个语音,通过注册算法生成个人的生物特征,将其嵌入到二维条码中,再打印条码到此用户的个人证件上。这样的证件具备了唯一、不易复制等特点,从而提高了证件的安全性能。对证件进行验证时,先用条码扫描设备读取条码中的特征数据,然后现场采集证件持有人的语音,进行比对,给出验证结果。

硬件的具体实现

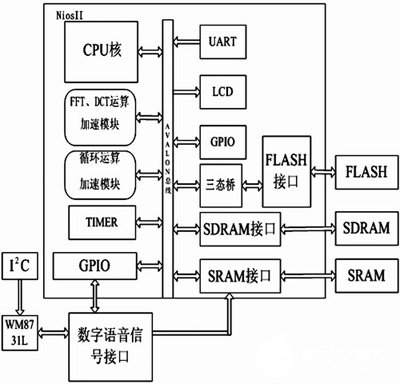

本设计以32位NiosII软核处理器为系统的核心部分,负责执行指令和数据运算。各种IP都可以通过SOPCBuilder连接到Avalon总线上,其中包含用户自定义的外设。用户外设的编写需要符合Avalon总线的规范。

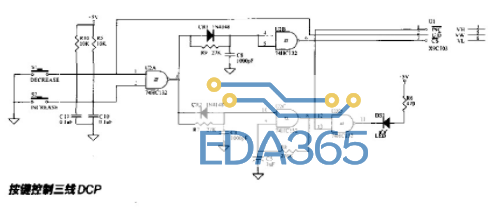

系统硬件结构如图2所示,包括CPU、UART、LCD、三态桥、片外存储器控制,以及各种输入/输出控制,这些IP都可以直接复用。这样的系统设计方法不仅模块化,而且大大缩短了系统设计周期。FFT运算模块不仅可以直接使用IP,还可以用C2H加速工具来提高系统性能。在此次设计中,FFT、DCT以及数据量较大的循环运算都采用C2H完成了硬件加速,效果较为明显。

图2系统硬件结构

NiosII软核处理器

NiosII是32位软核处理器,具有较高的性能。本设计在Altera的CycloneII上实现了处理器的配置,可以通过添加用户自定义指令来增强系统设计性能,同时可以添加多个片内存储器来提高数据的处理能力。

串口通信

本设计用到的扫描枪通过串口(UART)连接到开发平台上,目的是对二维条形码中包含语音特征的数据进行读取,通过Avalon总线将数据传送到相应的片外存储器中等待处理。

TImer

本设计利用SOPCBuilder工具将两个TImer挂到Avalon总线上。其中一个设置为在IDE中运行C程序时的系统时钟,另外一个用作计时器。算法程序中设置了多个时间戳(TImestamp),相邻两个时间戳内程序段的运行时间可以用这两个时间戳的差值来表示。时间戳的设置对程序运行没有影响。设置计时器的最终目的是:将完全的软件实现与用C2H加速后的程序运行时间进行比较。

语音采集和语音报告验证结果

系统中,语音采集和语音报告验证结果部分均由Wolfson公司的WM8731L完成。WM8731L可以独立于NiosII软核处理器单独工作,其控制模块可按照I2C总线的时序编写。WM8731L内部含有A/D、D/A模块,同时具备较高的采样率和量化精度。本设计采用了8kHz的采样率,16位的量化精度。

在语音采集部分,由于A/D是串行数据输出,因此编写了串行到并行数据转换以及写SRAM控制的Verilog模块。语音报告结果部分通过GPIO与CPU进行数据、地址通信,将不同的语音按照不同的验证结果播放出来,这些语音的数据已经事先烧写进FLASH中。GPIO的控制可以通过NiosIDE来完成。类似地,播放语音部分由于从FLASH读出的数据是并行的,因此编写了并行到串行数据转换的Verilog模块。

加速模块

首先,在NiosIDE下运行算法C语言程序,利用计时器找出程序运行的瓶颈环节。而后对瓶颈部分利用C2H工具进行硬件加速,从而提高系统性能。这部分主要包括FFT运算加速和循环运算加速模块。

软件流程

个人证件的验证流程如图3所示。验证分为两个基本过程,首先要读取条码中的数据,即用户登录;然后采集用户语音,即用户身份输入。经过特征比对,给出验证结果,由此可以说明用户现场所持证件是否属于其个人。

图3验证过程软件流程图

C2H硬件加速

NiosIIC2H加速器可以将ANSIC源程序代码转换成用户自定义的硬件加速模块。利用C2H工具,开发人员首先在AlteraNiosII处理器中开发和调试C语言算法,而后将分析出的C程序瓶颈代码转换成硬件加速模块。硬件加速模块被挂到Avalon总线上,作为用户外设来使用。由此实现了从软件运行算法到硬件加速处理的转换过程。需要注意的是,并不是所有的C代码都可以转换成硬件加速模块。C2H编译器的特点如下:

①支持大部分的ANSIC代码和C语言结构,如指针、堆栈、结构体、全局和局部变量、循环、函数调用等;

②C2H编译器可以将C语言的语法成分映射为硬件结构,而且用户可以控制这些硬件加速结构;

③由于IDE6.0整合了C2H工具,用户无需学习新的开发环境;

④C2H可以利用SOPCBuilder将加速好的硬件结构自动连接到Avalon总线上,无需用户手动处理;

⑤C2H可以产生硬件结构、资源利用率等详细报告。

本设计中规定用户采集语音的时长约为1s,内容为“你好”。在这样的条件下,利用计时器计算从预处理到给出识别结果的程序运行时间。系统时钟频率设置为50MHz。通过试验,得出运行时间约为5s,这显然不能满足实际需求。对实验结果进行分析,发现程序运行耗时主要集中在预处理和特征提取这部分,将其称为“前端”。经过分析前端的代码运行情况,设计师发现程序运行时间较长的主要原因是该部分包含了大量的矩阵运算和循环运算。下一步工作就是分析程序的运行瓶颈。经过分析研究发现,本设计算法中的瓶颈主要集中在加窗、FFT和DCT等部分,它们的耗时一般占到整个程序运行的60%以上。若将这些环节加速成功,性能将有较大提升。

图4中显示了在SOPCBuilder中向Avalon总线加载C2H加速器和片内RAM的情况。图中显示了两个加速器:accelerator_c2h_fft_fft和accelerator_c2h_fft_ham,分别对应FFT和加窗(汉明窗)的硬件加速运算过程,SOPCBuilder并没有为这两个模块分配基地址。图4中最下方的4个片内RAM可以起到数据缓存的作用。SinRAM与CosRAM为FFT加速运算提供正弦和余弦的查找表数据,dataRRAM与dataIRAM分别用于存储FFT运算后生成数据的实部和虚部。

图4C2H加速器和添加的片内RAM

gt是设计中同一用户注册时的3段语音(内容相同)。通过表1可以看出,完全软件计算时,FFT耗时大约为2s;利用C2H工具加速后,耗时仅约为0.01s,提速效果良好。而后再将算法程序中其它环节进行加速,则设计的整体性能是可以满足实际需求的。因此,C2H对运行在SOPC系统上软件算法的加速处理是十分有效的。

结语

本文阐述了一种基于FPGA平台的应用设计实例,不仅能充分体现SOPC设计理念,而且与生物特征技术有机结合,发挥了二者的优势,具有广阔的应用前景。另外,本设计采用了Altera的C2H加速工具对软件算法进行硬件加速,实验结果表明利用这种方法进行设计效果明显。由于使用C2H工具对算法有一定的限制,因此某些情况下,用户自定义指令和用户外设仍然是不可或缺的设计方法。这几种设计手段的有机结合是FPGA设计的主要方向。

责任编辑:gt

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多