来源:电子设计工程 作者:王庆龙 , 赵文元 , 王和国

1、引言

传统激光脉冲时间测距系统常采用模拟电路阈值检测实现时刻鉴别。这种方法比较简单,但受脉冲幅度变化的影响较大,且对信噪比要求很高。当信噪比很低时,则无法实现测距功能。因此不用门控电路控制脉冲计数,而直接利用高速数据采集器件及计算机进行数据采集和处理,可以获得大量的回波信息。面对高速率的传输数据,高性能FPGA的接口设计便成为连接前端A/D与后端信号处理器的纽带。

2、激光测距原理

在此仅讨论脉冲体制的激光雷达。作为一种非相干激光雷达,它采用的是脉冲法测距,即利用脉冲激光器发射一个或一列很窄的激光脉冲,通过测量回波与发射主波之间的脉冲延迟时间来测量距离(即测量飞行时间法)。在灵敏度足够和不产生测距模糊的情况下,其最大测量距离为:

R一=cTr/2=(C/2/fr=) (1)

式中:c是光速;Tr是激光往返于发射器和目标之间的传播时间,这里等于发射脉冲的重复周期;fc是激光发射脉冲的重复频率,用于确定回波脉冲是否到达的同步标志则决定了测距的准确度。对于利用计数脉冲计算光脉冲传播时间,其传播时间为:T=Tc·N=N/fc (2)

式中:N为传播时间内计数脉冲个数;Tc为计数器时钟周期;fc为计数器时钟频率。其目标距离为:R=cN/2fc (3)

由式(3)可知,fc越大,测量距离R精度越小。因此脉冲激光测距法的测距精度与计数脉冲时钟频率成反比,即时钟频率越高,测距精度也越高。

3、AT84AS004和XCL5VLX50简介

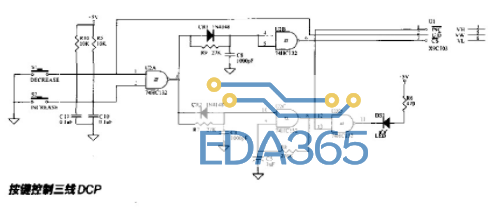

AT84AS004是由1:4的DMUX组成的10位2 Gs/s模数转换器,适用于满足第一或第二奈奎斯特采样定律的宽带信号的数字化。当它工作在2 Gs/s时,满足奈奎斯特第一定律会有7.8位的有效位和一55 dB的SFDR;满足奎斯特第二定律会有7.5位的有效位和54 dB的SFDR。1:4的多路数字信号输出是与LVDS逻辑兼容的,与标准的DSP和FPGA接口匹配,AT84AS004工作在2 Gs/s。由于A/D转换器AT84AS004集成度较高,模块设计相对简单。前端与运放采用差分输入方式,后端与FPGA内的4个双口RAM对应连接。采样速率为1 GHz,数据输出采用1:4并行模式,输出数据率为250 MHz,输入时钟和数据输出时钟类型可分别设置为CLK/2和DR/2,设置方法如图1所示。PCB设计可参考AT84A—S004一EB数据手册。

FPGA的选型主要基于高速和RAM资源丰富考虑目。由于XCL5VLX50的内核可工作在550MHz时钟吓,同时内部具有接近2 Mbit的RAM存储空间,能很好满足前端高速A/D数据采集和存储接口设计,同时也能满足高速数据吞吐率的要求。

4、激光脉冲测距雷达系统实现框架

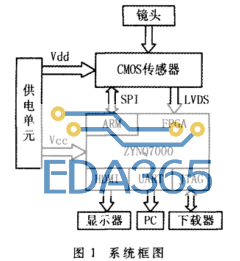

系统由高速运放、高速A/D转换器、低通滤波器、积累平均等功能模块组成。其中,低通滤波器可通过FPGA硬件完成,积累平均等功能模块可由高性能DSP组成。同时还需要有高速、高性能的FPGA构成MD转换器与FPGA和FPGA与DSP之间的高速数据接口。其信号流程是模拟信号首先通过运放AD8352差分放大送入AT84AS004内,输出分A,B,C,D 4个端口。当采样率为1 GHz时,采用同步输出模式的数据输出频率可达到125 MHz,再在FPGA内做相应处理,根据采样同步信号形成数据帧,分别送入TS一201的链路口L0"L3和总线DO~D63上。存入TS一20l片内RAM中并进行相关运算,然后通过链路口送入第2片TS一201中进行其他数据运算,数据结果通过与DSP相连的CY7C68013转换为USB协议数据或串口数据传到上位机。上位机软件采用VC语言,设计软件可识别USB接口,将距离数据读出并实时显示。A/D变换器时钟由AD9516产生,输入系统时钟或板上晶体振荡器时钟。图2所示为系统设计框图。

5、FPGA内部接口设计

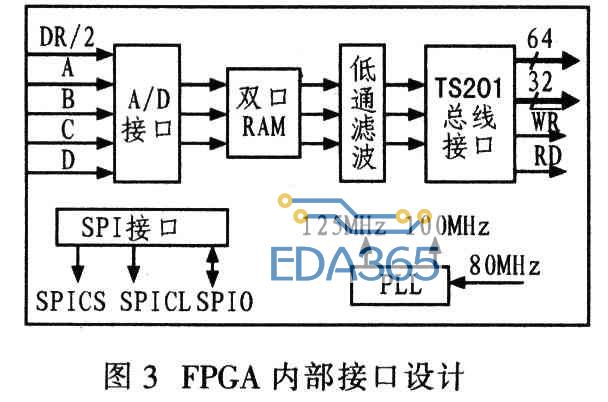

FPGA内部要求完成同步接收前端A/D采集的数据,并将数据进行低通滤波处理后转换为TS201链路口模式数据和总线模式数据,同时还要求模拟设计SPI端口完成时钟器件AD9516的初始化配置。与前端A/D接口设计采用4路同步锁存模式,同步接收时钟为125 MHz,上下沿触发,每路数据位宽为10 bit,将每路低位补零处理后拼成64 bit数据,各接口设计如图3所示。

6、 系统性能分析

6.1 采样率

为了能对激光窄脉冲实时采样,要求采样率达1 GHz。该方案采用E2V公司的高速A/D转换器AT84AS一004,其最高采样率可达2 GHz,提高了系统的升级能力,同时由于该器件具有多路转换功能,因而可大大降低数据传输速率,为系统硬件设计提供了条件。

6.2 数据传输率

由于A/D采样位宽为10位,当采样率为1 GHz时,其数据传输速率为10 Gbit/s,故对系统的吞吐能力提出了挑战。系统的吞吐能力完全取决于高性能ADSP TS201的链路口与总线的传输能力,当TS201系统工作在80 MHz时,链路口时钟工作在350 MHz时,总吞吐能力为13.52 Gbit/s,完全可以满足当前系统数据吞吐能力要求。而当采样率为1 GHz。系统采样时间为10μs,采样周期为1 ms时,可以在FPGA内部设计双口RAM,其缓存空间最大需要100 Kbit,而单独总线的传输速率在0.5 ms内就可达2.56 Mbit,链路口可作为系统升级为2 GHz采样率时备用。

6.3 测距精度

由于测距精度与计数脉冲频率成反比,当计数脉冲频率为500 MHz时,其理想情况下的最小测距精度可达0.3 m。

7 、结语

在给定测距范围内,测距系统无非追求两个重要指标:一是测距精度,二是实时性。当采用高性能FPGA作为激光窄脉冲处理核心框架后,系统在这两个指标上都具备软件处理上无可替代的硬性指标。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多