1 引言

无功补偿装置是用于补偿电网无功功率的不足,提高功率因数,保证供电系统安全运行和节约电能的设备,其核心是控制仪。本控制仪集无功补偿、电度量计量、电能质量监测及通信于一体,对电网参数进行实时采样与计算并把各项参数显示在LCD上,还可通过键盘进行系统参数设置,用于改变控制仪的运行模式等。

控制仪的最小系统由单片机80C196KC和可编程单片机外围接口芯片PSD834F2组成,这样既省去了地址锁存器和译码器等一些小规模芯片,使硬件电路得到了简化,又提高了系统的可靠性。系统运行所需要的程序、数据和参数均放在PSD834F2中。用复杂可编程逻辑器件(CPLD)取代一些数字器件扩展系统的外围电路,进一步提高了系统的性能,还便于调试和维护。本文以下将具体介绍如何用CPLD来扩展键盘和显示电路。

2 键盘输入模块的硬件设计

键盘输入主要用于现场电流变比,电容器组数,单组电容器容量,电压上、下限,谐波上限,控制仪地址编号等系统参数设置。而且与显示模块配合用于查看各相电压、电流,无功功率,有功功率,功率因数等的情况。

设计键盘时,如果采用软件扫描的方式,虽然硬件电路简单,但扫描会耗去CPU不少时间,降低系统的整体性能;如果采用接口芯片8279来管理键盘,虽可代替CPU完成对键盘的控制,减轻CPU的负担,但8279体积大且功能单一。所以,本系统采用复杂可编程逻辑器件(CPLD)来设计键盘的接口电路,完成对键盘的扫描工作,当有键按下时,则产生中断信号供CPU读取扫描码。除此之外,CPLD还可实现其它模块的接口电路以及完成地址译码等功能。

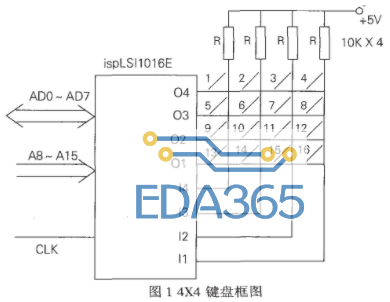

本系统采用4X4键盘,其硬件电路如图1:

图1 4X4 键盘框图

CPLD采用Lattice公司的ispLSI1016E-100L器件,该器件包括32个I/O引脚,4个专用引脚,集成密度为2000个PLD等效门,引脚至引脚的延迟为7.5ns,工作频率为100MHz。该器件由集总布线区(GRP)和万能逻辑块(GLB)构成,GLB通过GRP连接起来。[page]

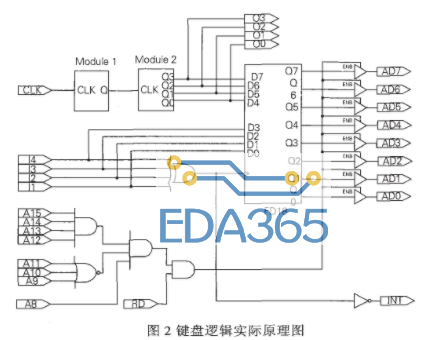

对复杂可编程逻辑器件(CPLD)内部逻辑功能的描述方式有多种,本系统采用了原理图输入与VHDL语言描述相结合的方式,这样可以发挥两者的优势,加快开发进程。设计时采用层次化设计,描述系统总体功能的最上层使用原理图输入,而原理图中的某些功能模块采用VHDL编写。实际原理图如图2:

图2 键盘逻辑实际原理图

上图中Module 1模块实现分频功能,CLK来自单片机80C196KC的CLKOUT脚,其周期为3个时钟振荡周期,占空比为33%。若单片机用16M晶振,其频率约为:16M/3=5.33M。Module 1 把频率降至约1K,Module 2模块以一秒的间隔使O3~O0依次循环输出低电平进行键盘扫描 。当有键按下时,I3~I0中有一个为低电平,异或门输出1个高电平脉冲,锁存键盘状态并向单片机申请中断。系统为键盘分配的地址空间为0xf100~0xf1ff,在此范围内可读取键盘的扫描码。

由于篇幅有限,以下只给出Module 2的VHDL语句,具体如下:

LIBRARY ieee;

USE ieee.STd_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY Module2 IS

PORT ――定义端口

( clk :IN std_logic;

q :OUT std_logic_vector(3 DOWNTO 0)

);

END Module2;

ARCHITECTURE Module2 of Module2 IS

BEGIN

PROCESS(clk)

VARIBLE sum:integer:=0; ――定义变量sum,初值为0

BEGIN

IF(clk’event AND clk=’1’)THEN

sum:=sum+1; ――clk为上升沿时,sum加1

IF(sum》=5)THEN

sum:=1;

END IF;

END IF;

CASE sum IS ――根据sum输出相应的值

WHEN 1 =》 q《=“1110”;

WHEN 2 =》 q《=“1101”;

WHEN 3 =》 q《=“1011”;

WHEN 4 =》 q《=“0111”;

WHEN THERS =》 q《=“1111”;

END CASE;

END PROCESS;

END Module2;[page]

3 键盘扫描码与相应键的对应关系

中断服务程序读取寄存器FD18中的扫描码,经过判断就可知道按下的是哪一个键,然后转入相应的程序进行处理。键号和扫描码的具体对应关系如表1:

表1 键号和扫描码对应表

4 键盘输入模块的软件设计

系统的一些基本参数可以通过键盘来设置或改变,每按下一键,CPLD扫描到键值后向CPU申请中断。CPU进入键盘管理中断程序后,读取、存储键值并置接收到键值标志。主程序识别到标志,对接收到的键值进行处理。

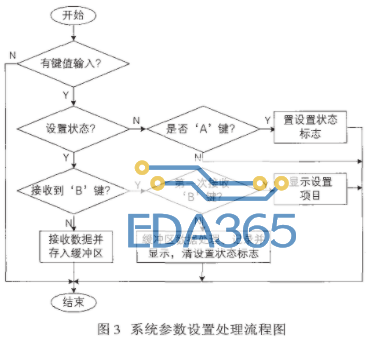

参数设置格式是:A**B**…*B。也就是说,按‘A’键进入设置状态,‘**’的组合表示设置项目,‘B’确认设置项目,‘**…*’所设置项目的数值,最后的‘B’是结束符,表示此次设置结束。设置步骤的软件处理流程如图3:

图3 系统参数设置处理流程图

5 结束语

用复杂可编程逻辑器件(CPLD)扩展的键盘接口经过实用,效果较好,既提高了单片机的响应速度,又简化了硬件电路。此外,CPLD还可用于其它的接口设计,使其性能得到进一步体现。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多