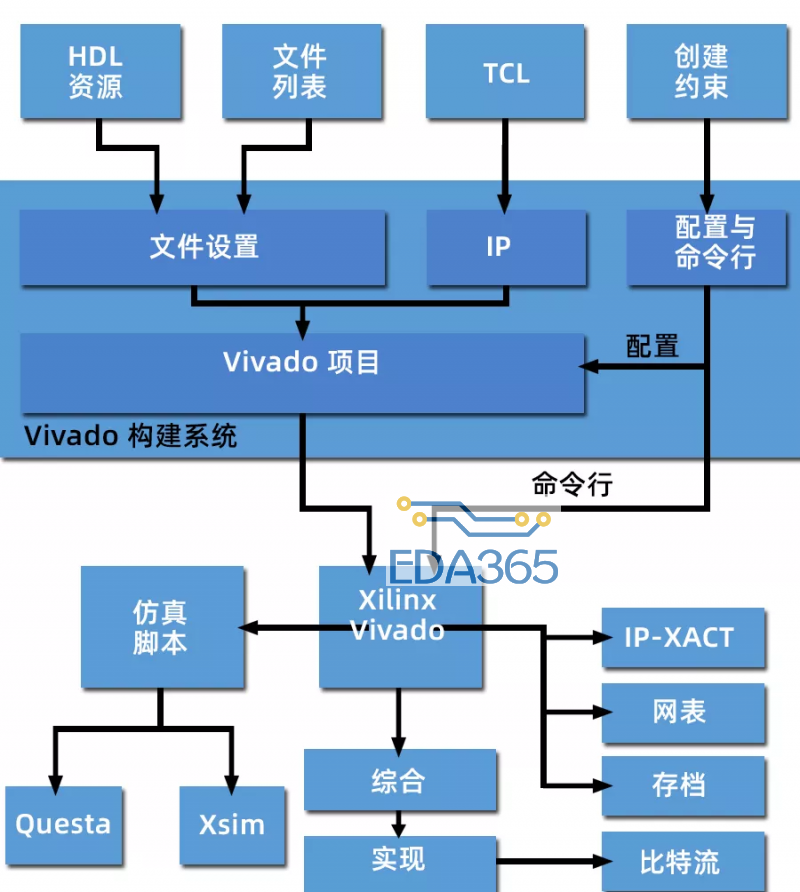

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。Vivado 工具非常适用于这类工作,因为该工具能够为项目生成存档文件或创建 TCL 文件,从而再现项目状态。

然而,上述机制需要一定数量的手动操作,而且在 Vivado 设计套件项目外对设计的参数进行设置,也存在不够灵活的问题。因此,为了简化上述操作,我们已经开发出对应脚本。其思路是在提供项目的 HDL 和 TCL 源文件的同时,提供从头创建 Vivado 设计套件项目所需的其他配置文件。设计构建脚本的目的是帮助用户在单独的 Vivado 设计套件项目下开发独立的项目组成部分(特色),且能够以其他配置方式对项目不同组成部分的源文件进行组合。此外,构建脚本也可用于创建目标构建工件,例如 IP XACTIPXACT 封装、仿真、综合、实现和比特流生成。

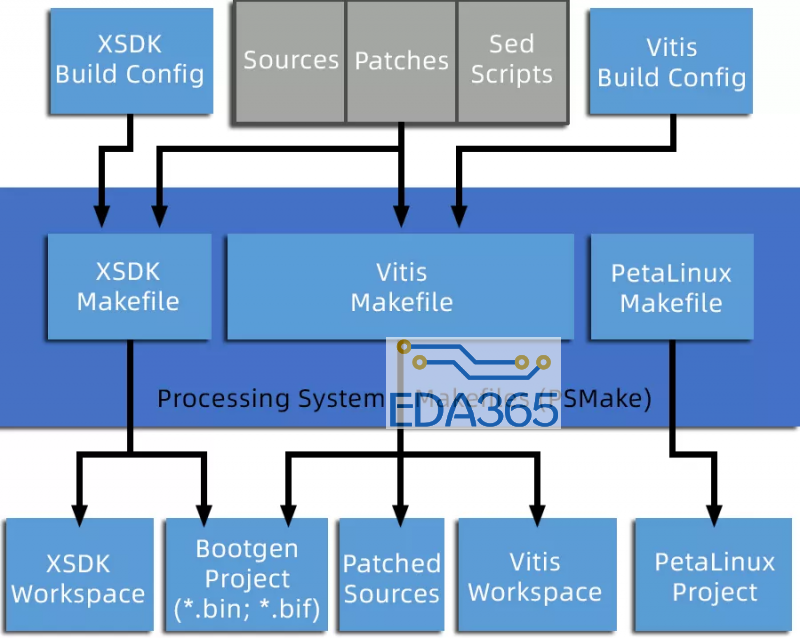

与此同时,MLE 也面向 PetaLinux 和赛灵思软件开发套件 (XSDK) 发布了一套易用型 Makefiles,并将为 Vitis™ 统一软件平台提供后续支持。这些处理系统 Makefiles(或简称为 PSMake)还提供在 GitHub 上。

为了加快实现 FPGA 构建环境的自动化(如用于持续集成 (CI)),并确保在开发与生命周期后期阶段完整重现设计结果,Missing Link Electronics 团队已整合出一套脚本。目前,这套脚本化 FPGA 构建环境主要面向赛灵思 Vivado 工具(版本 2016.4 或更新版本),并在 Ubuntu Linux 16.04 LTS 和 18.04 LTS 下通过测试,已通过 Apache 2.0 开源许可证提供在 GitHub 上。

APP下载

APP下载 登录

登录

热门文章

热门文章