摘要:为了适应机载液晶显示器向低功耗、高集成度发展的趋势,提出了一种基于Zynq可扩展处理平台的图形生成电路实现方法。方法以Zynq为核心搭建硬件平台,使用Zynq集成的ARM 处理器执行图形生成算法运算,配合可编程逻辑资源,按照一种三缓冲机制对DDR3SDRAM 帧存数据进行缓冲处理,实现图形的实时生成.采用本设计可以生成多种分辨率的机载图形画面.实验结果表明,当生成分辨率为1024×768的EFIS电子飞行显示系统画面时,帧率可达74fps,能够满足机载液晶显示器高性能实时显示需求。

1 引言

在飞机座舱显示系统中图形显示占据重要地位[1].主显示器尺寸不断加大,分辨率不断提高,并日益朝着大屏幕化、综合化、信息化和智能化方向发展[2].随着分辨率的提高,要显示的信息量也大幅增加,座舱图形综合显示系统是一个对实时性要求很高的系统[3],军用飞机在做战术动作时,画面变换速度快,要求图形的更新速度也必须很快,至少要比帧或场的刷新速度快,才可以避免画面的断续[4G5].采用DSP+FPGA 的图形硬件加速架构,或者使用专用GPU 图形生成芯片,都可以生成高分辨的机载显示器图形,但随之而来的是产品成本的急剧增加以及功耗的不断上升[6].为机载图形显示系统配置更合理的硬件设计和软件架构变得尤为迫切。

Xilinx最新平台Zynq将处理器的软件可编程能力与FPGA 的硬件可编程能力实现完美结合,以低功耗和低成本等系统优势实现良好的系统性能、灵活性和可扩展性[7].本文提出一种基于Zynq可扩展处理平台的实时图形生成电路,利用Zynq内部集成的ARM 处理器以及可编程逻辑资源,实现了机载显示器图形画面的实时生成与显示。

2 Zynq简介

2.1 Zynq构成

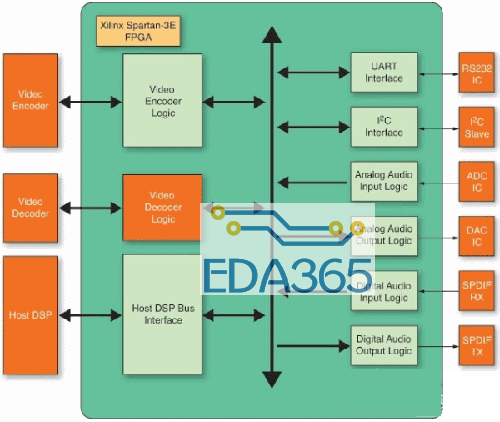

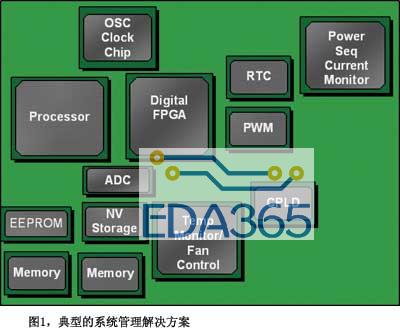

Zynq构架将内部结构分为处理器系统(ProcessingSystem,PS)与可编程逻辑(ProgrammableLogic,PL)两部分[8].PS部分包括双ARM CortexGA9内核、存储器接口以及通用外设接口等资源.PL部分也即常规的FPGA,通过PL生成的IP核可以作为ARM 内核的扩展外围设备或者ARM 内核的加速部件.Zynq器件内部结构图如图1所示。

.jpg)

图1 Zynq内部结构图

Zynq架构可以对PL和PS中运行的自定义逻辑和软件方便地进行管理和规划,PS和PL的单芯片综合使其在I/O 数据带宽、功能耦合、功耗预算等方面的性能表现大大超越了以往ASSP和FPGA 双芯片解决方案。

PS和PL可以通过多种途径实现互联,包括GPIO端口、AXI总线端口、EMIO 端口、中断、DMA 等等.其中AXI总线是ARM 系统中连接各个模块的主要通道,各个功能部件通过AXI总线实现互联.在PL中可以通过工具自动生成带有AXI接口的IP 核,和PS 端进行高速数据交互。

2.2 DDR Memory控制器

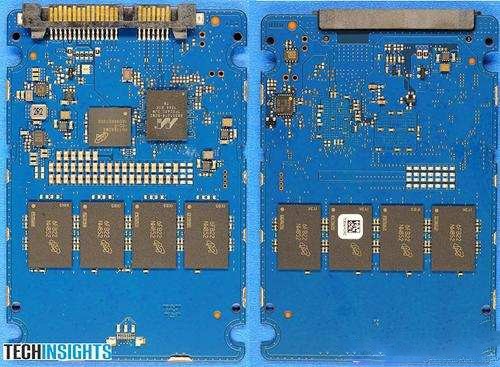

Zynq内部集成的DDR memory控制器支持DDR2、DDR3、LPDDR2等多种存储器类型,包含了3个主要模块:AXI存储器端接口DDRI、带有传输调度机制的中央控制器DDRC 和物理层控制器DDRP[9].DDRmemory控制器框图如图2所示。

.jpg)

图2 DDR Memory控制器框图

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多