描述:在此项测试中,发起四次读写访问,其中读写操作分别间隔开,四次读写操作访问的地址都是同一个,由此观察读写切换引入的带宽开销。由图可见,在执行完一次读/写操作后,即使下一次写/读操作的地址不变,也不能立即执行下一个命令,必须等待一段时间。经测量,发现在连续的读写切换过程中,一组读写操作所需总时间为8000ps+23508ps+8000ps+40492ps=80ns,其中有效时间为16ns,带宽利用率为20%。

图6 相同Bank同一行读写切换时序图

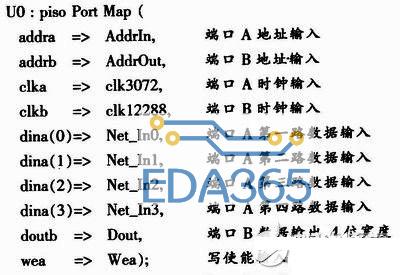

描述:在此项测试中,发起四次读写访问,其中读写操作分别间隔开,四次读写操作访问的地址在相同Bank的不同行,由此观察读写切换引入的带宽开销。由图可见,由于读写切换以及行切换,在连续的读写切换过程中,一组读写操作所需总时间为8000ps+35508ps+8000ps+76492ps=128ns,其中有效时间为16ns,带宽利用率为12.5%。

图7 相同Bank不同行读写切换时序图

经过上面若干测试项的验证,可以发现:Xilinx的DDR3控制器结合DDR3芯片对于按地址连续存储,效率还是比较高的,基本上可以达到95%以上(一些零散的开销未详细计算,故取5%作为这些开销的总和)。但Xilinx的DDR3控制器对DDR3的随机地址存取效率比较低。对于一些查表应用,由于查表地址是随机的,DDR3的存取效率是很低的。

造成随机存取效率较低的原因主要有:1.同Bank行切换;2.同时打开的Bank数只能是4个;3.读写切换。

随机存取DDR3带宽利用率基本维持在11.8%-40%之间。

1.将Xilinx的DDR3控制器的同时能打开的bank数改为8;

2.调整DDR3访问(读或写)的顺序,避免同Bank行切换以及读写切换。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多