关于chipscope中各模块的说明、调用等方法在以上的参考资料中都有详细说明,在这里就不详细叙述了。在此仅以一个简单的例子为例,说明一下我在ISE中直接调用chipscope Pro Analyzer进行在线逻辑分析的实现方法。

首先在ISE中建立一个工程,并输入如下的代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 21:26:06 02/26/2010

// Design Name:

// Module Name: mycounter

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module mycounter(

input clk,

// input reset,

output sout

);

reg [19:0] cnt=0;

always @(posedge clk)begin

/* if(!reset)

cnt<=0;

else*/

cnt<=cnt+1;

end

assign sout=cnt[19];

endmodule

这里为了简单起见,把同步复位等信号也给屏蔽掉了。我使用的是自制的Spartan3的板子,其中FPGA选择Xilinx公司的XC3S400-TQC144G;PROM 选择Xilinx公司的XCF02SV0G20C,FPGA的时钟管脚是P55;ISE套件使用的12.2版本。然后在PlanAhead中分配I/O管脚如下:

# PlanAhead Generated physical constraints

NET "clk" LOC = P55;

//NET "reset" LOC = P11;

NET "sout" LOC = P12;

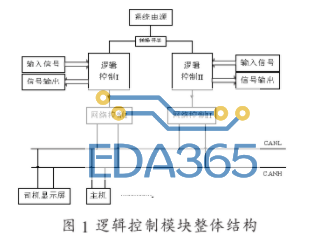

接下来对代码进行综合,无误之后开始创建Chipscope的核。首先在ISE Project Navigator中点击Project---New Source Wizard,选择Chipscope Definition and Connection Wizard,输入文件名,并一直点Next生产.cdc文件,如图1所示。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多