Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),Verilog HDL语言是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL和VHDL是目前世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准

Verilog HDL语言学习用途就是在最广泛的C语言的基础上发展起来的一种件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL成为IEEE标准,即IEEE Standard 1364-1995.

Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。与之相比,VHDL的学习要困难一些。但Verilog HDL较**的语法,也容易造成初学者犯一些错误,这一点要注意。

硬件描述语言是一种形式化方法描述数字电路和系统的语言。数字电路,应该是在大二上学期左右学习的课程,是一门非常重要的课程。现在大学的可能主要集中在逻辑门和小规模集成电路的讲解上,很少涉及到HDL。当然,我们是可以通过一些列的74系列芯片构成我们想设计数字系统,但是当系统门数增多,设计就会变得非常复杂和困难——但是照样有老外用这个方法实现了8位处理器,不过说实话,其成本和消耗的精力只能用来赚点眼球效应,而没太多的实际意义。

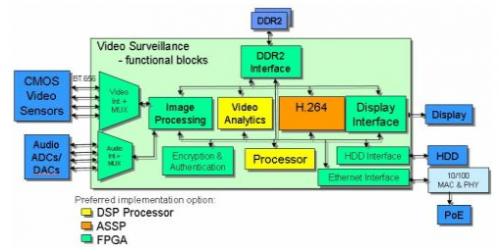

随着EDA技术发展,现在更多的是采用CPLD、FPGA、ASIC等来实现。首先采用HDL由抽象到具体、逐层描述设计思想,最后利用EDA工具进行仿真、综合,转换成门级电路网表,接下来再用CPLD/FPGA/ASIC自动布局布线工具把网表转换成具体电路布线结构的实现(这个概念可能对新手有一定难度,打个比方就好像是选了一堆适用的74芯片,然后再进行了连线)。

现在的数字系统和数字信号处理发展相当快,掌握一门HDL,是理工科大学生的一个基本技能,现在的趋势是甚至比掌握单片机更加重要。因为我们使用HDL,甚至可以自己编写一个自己的单片机出来,然后在FPGA/ASIC上实现。

硬件描述语言的发展至今已经有20多年的历史。现在主要的语言VHDL(Very High Speed Integerated Hardware Description Language)和Verilog HDL(Verilog Hardware Description Language)适应了历史发展的趋势和要求,先后成为IEEE标准。

由我看来,语言的出现就是用语言描述替代图形化(元件拼凑)设计,把我们要实现的功能和思想用语言的形式写出来,转换成实际电路的工作就交给EDA工具去做,从而简化了我们设计的工作,节约了开发的时间。也可以这么说,对于硬件不是特别明白的人也不必要去了解过多的关于电路的东西就可以开始做开发,对于科研人员可能更为有用。

选Verilog还是VHDL学习,这个问题有很多的争论。

这个东西好像蛮重要的,因为刚开始就要选定用什么语言,要比较两种语言的优劣,使用的情况等等,以后才能更好的学习。我只会Verilog,所以不敢乱弹两者之间的优劣,想从另外一个角度来说一下。

这两种语言都是用于数字电子系统设计的硬件描述语言,而且都已经是IEEE的标准。VHDL 1987年成为标准,而Verilog是1995年才成为标准的。这个是因为VHDL是美**方组织开发的,而Verilog是一个公司的私有财产转化而来的。为什么Verilog能成为IEEE标准呢?它一定有其优越性才行,所以说Verilog有更强的生命力。

这两者有其共同的特点:

1.能形式化地抽象表示电路的行为和结构;

2.支持逻辑设计中层次与范围地描述;

3.可借用高级语言地精巧结构来简化电路行为和结构;具有电路仿真与验证机制以保证设计的正确性;

4.支持电路描述由高层到低层的综合转换;

5.硬件描述和实现工艺无关;

6.便于文档管理;

7.易于理解和设计重用——这点很重要啊!

但是两者也各有特点。Verilog HDL推出已经有20年了,拥有广泛的设计群体,成熟的资源也比VHDL丰富(但是好像我在找资料的时候都是VHDL的资料多一些,这个和现在的氛围有关)。Verilog更大的一个优势是:它非常容易掌握,只要有C语言的编程基础,通过比较短的时间,经过一些实际的操作,可以在2~3个月内掌握这种设计技术。而VHDL设计相对要难一点,这个是因为VHDL不是很直观,需要有Ada编程基础(我都不知道是什么,晕了),一般认为至少要半年以上的专业培训才能掌握。

目前版本的Verilog HDL和VHDL在行为级抽象建模的覆盖面范围方面有所不同。一般认为Verilog在系统级抽象方面要比VHDL略差一些,而在门级开关电路描述方面要强的多。

近10年来,EDA界一直在对数字逻辑设计中究竟用哪一种硬件描述语言争论不休,目前在美国,高层次数字系统设计领域中,应用Verilog和VHDL的比率是80%和20%;日本和台湾和美国差不多;而在欧洲VHDL发展的比较好。在中国很多集成电路设计公司都采用Verilog,但VHDL也有一定的市场。

夏宇闻老师推荐应该先学Verilog,然后再学习VHDL。我觉得也是,只会一门语言是不够的,否则在交流上会出现问题,而且用原理图的方法设计数字电路也是一个必备的能力,否则不能软硬通吃,达到大牛的水平啊。

大学里面有的学校会讲述VHDL,但是并不妨碍学习Verilog。

这个问题,可能不同的人回答有不同的答案,每个人推荐的书也不一样。不过关于Verilog,夏宇闻老师绝对是中国的泰斗级人物,我推荐的几本书都和他有一定的关系。这个不是因为我个人和他关系好,而是确实这几本书不错。我建议大家最好有纸版的书,一个方面是支持夏老师的辛勤工作,另外一个方面也是便于阅读和学习。

(1)没有学过数字电路的同学,建议首先购买一本STEPHEN BROWN编写、夏老师翻译的《数字逻辑基础与VERILOG设计(原书第2版)》。这本书在【Altera FPGA/CPLD资料专版】有电子书可以下载。本书可以作为数字电路的课本,也讲了Verilog的,是一本不可多得的好书。本来我这个学期准备在学校以这本书为教材开全校选修课的,结果领导不知道什么原因把这个课给卡擦了……

(2)有没有学过数字电路的同学,都应该有一本《Verilog HDL数字设计与综合(第二版) 》,该书由Samir Palnitkar 编著,夏老师翻译。该书的英文原版被视为Verilog的经典著作,美国很多大学的研究生课程的课本,中文版我也看了一部分,觉得还是不错的书,【Altera FPGA/CPLD资料专版】有中英文两个版本的电子书。网上有很人攻击这本书翻译的不好,不过看了那些评论和书之后,自然有定论,流言自然会不攻自破。

(3)第三本是夏老师编著的《VERILOG数字系统设计教程(第2版)》。这本书在Altera FPGA/CPLD资料专版】有下载,我看过第一版我没看过,现在这本书还经常翻翻,都已经被我弄得非常破旧了。这本书刚出来的时候国内还没有很好的Verilog方面的书,我是托人在北京帮我买的(那会儿好像网上书店还没有呢)。书中对于语法和实际应用都讲的非常非常好,强烈建议大家好好阅读和学习。

书就推荐这么多,可能还需要一些资料,否则光是语言,没有实战,不容易有实际的感受。后面我还会推荐一些资料和某些书的一些章节,到了具体的地方再说。

在学习语言的同时,我觉得应该要学习硬件的使用,毕竟我们是为了设计硬件电路才学习语言的。在本站的教程专版有相应的硬件工具,可以从本站购得PCB自己焊接,也可以自己制作相应的电路模块进行学习。

硬件上必须要花一些钱,不能总是觉得有些东西好像很贵,舍不得。其实现在更多的人宁愿把钱花在玩游戏、吃吃喝喝,也不肯把钱花在学习上。我很喜欢那种自己去找办法学习知识,自己买硬件或做硬件学习的学生。我遇上这样的学生,有时候还会主动给他们硬件来学习。而对于那种有惰性的学生,我觉得可能没几个老师会喜欢的。

Altera公司的Quartus II,设计软件。

Mentor Graphics公司的ModelSim,仿真软件,Altera的软件里面也有相应的AE版本。

其它的一些综合工具、程序编写工具,可以等到学习的差不多了再弄。

软件的使用,我觉得最直接的方法是看厂商的Help,其次就是上面提到的有两本书的附录中也有相应的资料。

DE2板子的10个例子,在【FPGA与SOPC设计教程:DE2实践 】这本书的第六章有中文版的翻译,大家可以到下载区找这本书。

其它的学习资料或教程——我也准备写这么个东西,但是一直在思考是该从编程、硬件应用还是数字逻辑的角度来进行讲述,迟迟没有动笔是因为把握不好方向,一旦方向错了,会让很多人走弯路,我可负不起这个责任。

其实,资料并不在多,关键是精,另外一个就是找的资料一定要看,不要以自己有多少资料为荣,应该是以自己看了多少资料为荣。

学习的过程,每个人都不太相同。我以个人经验随便说两句吧。

首先是软件的使用,比如QuartusII的使用应该放在所有的学习之前(学过数字电路的同学,如果没有学过的话,先把一些基本概念学一下,在学习到《数字逻辑基础与VERILOG设计》的时候开始用原理图设计的方法学习使用该软件),然后就是学习Verilog了,建议在学习的过程中把书中的例子都用软件做一次,也利用Quartus提供的仿真功能进行仿真。

基本的语法知识学习的同时,书上很多仿真的例子在Quartus里面并不能实行,这个时候就需要学习使用ModelSim了。

进一步学习Verilog的高级编程知识,利用软件多做一些例子程序。

上面推荐的后两本书看的差不多的时候(夏老师那本书的中级篇CPU设计之前的内容,另外那本第一部分结束),就可以到板子上编一些实际的应用程序了。这个时候就可以参考DE2那本书的几个例子,或者是参考电路板上的硬件,针对不同的部件进行编程和验证。

然后就是根据自己的兴趣爱好和专业方向,找一个题目用Verilog去实现(或者找相关的老师,看他们手上有没有这样的方向,你可以去帮忙做点什么的),这个过程中需要学习更多其他方面的知识,这样才能做成真正的应用系统。

这个时候可能手上的CPLD的资源可能就不那么够了,也许就该用FPGA来做了。此外FPGA和CPLD还是有区别的,两个器件应用的场合有所不同,这个在学习的过程中也要逐步积累这些知识和经验。此外,还可以学习一些SOC方面的知识,这里不仅仅是指的Nios II。

后面继续学习,不断学习,持续学习——学习是一辈子的事情,不是花上那么几个月你就能把所有的技能学到手,更多的时候是通过实践不断提升自己的能力,这就是所谓的实践出真知。我想从大二开始学习到大三结束,两年的时间基本能掌握这门技能,大四的毕业设计应该可以做出自己的优秀设计来。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多