数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

1.组合逻辑概念

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关,不涉及对信号跳变沿的处理,无存储电路,也没有反馈电路。通常可以通过真值表的形式表达出来。

2.组合逻辑的Verilog HDL 描述

根据组合逻辑的电路行为,可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。

(1)always 模块的敏感表为电平敏感信号的电路

always模块的敏感列表为所有判断条件信号和输入信号,但一定要注意敏感列表的完整性。在always 模块中可以使用if、case 和for 等各种RTL 关键字结构。由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”。always 模块中的信号必须定义为reg 型,不过最终的实现结果中并没有寄存器。这是由于在组合逻辑电路描述中,将信号定义为reg型,只是为了满足语法要求。

(2)assign语句描述的电路

利用条件符“?”可以描述一些相对简单的组合逻辑电路,信号只能被定义为wire型。当组合逻辑比较复杂时,需要很多条assign语句或者多重嵌套“?”,使得代码可读性极差,因此此时推荐第一种组合逻辑建模方式。

3.组合逻辑电路的注意事项

(1)敏感信号列表

在组合逻辑设计中,读者必须重点对待敏感信号列表。敏感信号列表出现在always块中,其典型行为级的含义为:只要敏感信号列表内的信号发生电平变化,则always模块中的语句就执行一次,因此设计人员必须将所有的输入信号和条件判断信号都列在信号列表中。

不完整的信号列表会造成不同的仿真和综合结果,因此需要保证敏感信号的完备性。如果缺少信号,则无法触发和该信号相关的仿真进程,也就得不到正确的仿真结果。如果设计人员在设计中,认为列举信号麻烦,则采用下面的语句:always@(*).此时,综合工具和仿真工具会自动将所有的敏感信号自动加入敏感信号列表。

(2)不要在组合逻辑中引入环路

在组合逻辑中引入环路会导致电路产生振荡、毛刺以及冲突等问题,从而降低设计的稳定性和可靠性,因此要彻底避免环路。

之所以称逻辑环路是一种高风险设计,其原因如下:

首先,环回逻辑的延时完全依靠组合逻辑门延迟和布线延迟。一旦这些传播时延有所变化,则环路的整体逻辑将彻底失效。

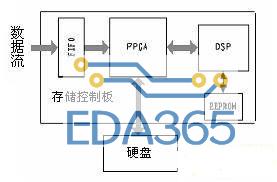

其次,环路的时序分析是个死循环过程。目前的EDA 开发工具为了计算环路的时序逻辑都会主动割断时序路径,引入许多不确定的因素。

1 . 时序逻辑概念

时序逻辑是Verilog HDL 设计中另一类重要应用。从电路特征上看来,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。电路里面有存储元件(各类触发器,在FPGA 芯片结构中只有D 触发器)用于记忆信息,如图8-7 所示。从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

(1)在描述时序电路的always块中的reg型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

(2)时序逻辑中推荐使用非阻塞赋值“<=”。

(3)时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的。

2. 竞争与冒险

(1)竞争与毛线概念

信号在组合逻辑电路内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。此外,信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为“毛刺”,如果一个组合逻辑电路中有“毛刺”出现,就说明该电路存在“冒险”。

需要注意的是,冒险信号的脉冲宽度很小,常常只有数纳秒或数十纳秒,其频带带宽可达数百兆赫兹或更宽。在板级调试时,如果示波器的上限频率较低,会将幅度较大的毛刺显示为幅度较小的毛刺,甚至不易被察觉。这都是在实际开发中捕获毛刺应该注意的问题。

冒险按产生形式的不同可以分为静态冒险和动态冒险两大类。静态冒险是指输入有变化,而输出不应变化时产生的单个窄脉冲;动态冒险则指的是输入变化时,输出也应变化时产生的冒险。动态冒险是由静态冒险引起的,因此存在动态冒险的电路也存在静态冒险。

静态冒险根据产生条件的不同,分为功能冒险和逻辑冒险两大类。当有两个或两个以上输入信号同时产生变化时,在输出端产生毛刺,这种冒险称为功能冒险。如果只有一个变量产生变化时出现的冒险则是逻辑冒险。冒险往往会影响到逻辑电路的稳定性。清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。

(2)冒险产生的原因

由于动态冒险主要是由静态冒险引起的,消除了静态冒险,动态冒险也就自然消除了,因此下面介绍静态冒险的检查和消除。

判断一个逻辑电路在某些输入信号发生变化时是否会产生冒险,首先要判断信号是否会同时变化,然后判断在信号同时变化的时候,是否会产生冒险,这可以通过逻辑函数的卡诺图或逻辑函数表达式来进行判断。

(1功能冒险的检查

功能冒险是由电路的逻辑功能引起的,只要输入信号不是按照循环码的规律变化,组合逻辑就可能产生功能冒险,且不能通过修改设计加以消除,只能通过对输出采用时钟采样来消除。

(2逻辑冒险的检查

检查电路是否产生逻辑冒险的方法有两种,即代数法和卡诺图法。

① 代数法。如果一个组合逻辑函数表达式F,在某些条件下能化简成或的形式,在A产生变化时,就可能产生静态逻辑冒险。

② 卡诺图法。在组合逻辑的卡诺图中,若存在素项圈相切,则可能会产生逻辑冒险。如图8-16 所示的卡诺图,AC 和两个素项环相切,在B = C =1时,A 由1 变为0时,将产生逻辑冒险。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多