我学verilog语言进行FPGA设计也就半年时间,很多的东西就是在网上学到的,现在想说说自己对使用verilog进行FPGA设计的一些体会,我水平不高,主要是为新手朋友们介绍自己的一点经验少走点弯路。

1、verilog语言

学习verilog最重要的不是语法,“因为10%的语法就能完成90%的工作”,verilog语言常用语言就是always@(),if~else,case,assign这几个了,不用去专研繁杂的语法,有些问题等你碰到了查查书就好了。这里推荐夏雨闻老师的《verilog数字系统设计教程》,一本很适合新手的好书。

2、硬件原则

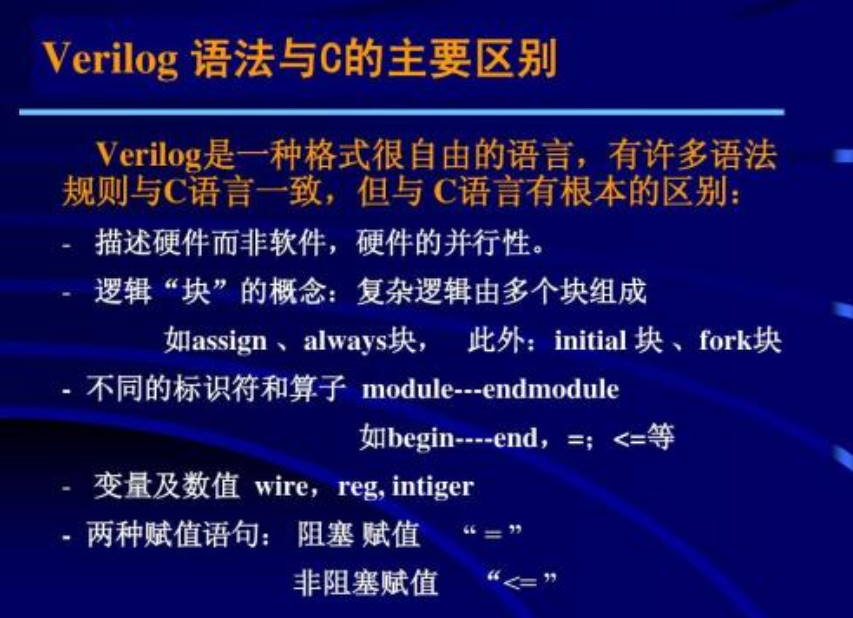

虽然verilog语言很象c语言,但它和c语言还是有本质的区别的,因为verilog进行的是硬件设计,你写出来的东西是实实在在电路,所以要有数字电路的知识是肯定的。数字电路就是由时序电路(触发器)和组合逻辑电路(各种逻辑门)构成的,用verilog写的程序在FPGA实现就是触发器和逻辑门,所以最重要的就是“你对你写的语言生成的电路心中有数”,做到这一点你就不会有写出来的程序不能综合的麻烦,电路的冗余逻辑肯定也是最少的。还要注意一点就是verilog程序是并行的,不是象c那样是顺序执行的,这是因为fpga硬件可配置,可形成不同的任务单元同时工作;而单片机这种基于通用目的,硬件结构也固定了,它处理任务只能一件一件顺序的进行。

3、同步原则

在进行FPGA设计的时候,同步原则应该是最重要的原则之一了,因为异步电路的不可控性,很可能有毛刺产生,而在芯片内部的任何一点毛刺都会一级一级的传递下去,最终影响系统的稳定性。同步原则用一句话来总结就是“不要试图产生自己的时钟”,最好一个设计或者一个模块只使用同一个时钟,这样所有的触发器都在同一个时钟沿跳变,当然最稳定了,系统也能跑到很高的速度。一个小技巧就是多使用触发器的使能端和取沿电路。

4、养成好的代码习惯

很多的细节,比如缩进、命名、参数化、组合逻辑和时序逻辑分离、注释等等,也就是大家说的代码风格。这个其实很重要,最好在一开始就养成好的习惯,这样会为你以后的工作节省很多时间,也会大大提高工作的质量。不注意这个将很吃很多的苦头 ,细节决定成败啊。

5、工具

工具永远就是工具,最重要的是学会怎么使用它,不用去研究它,用的多了自然就熟练了,遇到那个问题了自然就会去找到问题的答案,不用开始就抱着工具的手册狂看,问问别人很简单的。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多