PLL(锁相环)频率合成通过锁相环完成频率的加、减、乘、除运算。该方法结构简单、便于集成,且输出频率高、频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。DDS(直接数字合成)是近年来迅速发展起来的一种新的频率合成方法。这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,缺点是输出频率不能太高。如果把两者结合起来,用DDS的输出作为PLL的参考信号,就能满足现代电台对频率合成器的设计要求。本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

1 DDS的结构及工作原理

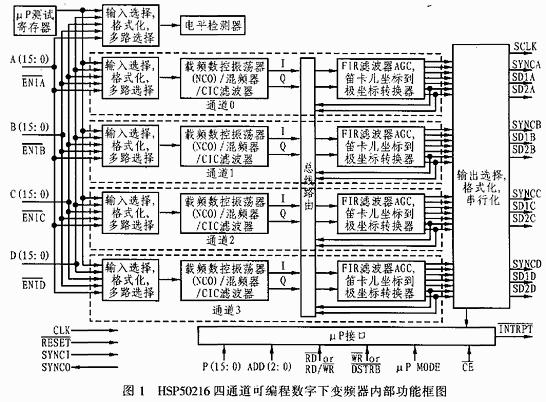

DDS的基本结构由参考时钟、相位累加器、ROM、DAC(数模转换器)和LPF(低通滤波器)组成,见图1。

DDS的工作原理是:在参考时钟fr的控制下,频率控制字K由累加器得到相应的相位数据,把此数据作为取样地址,来寻址正弦ROM表进行相位-幅度变换,输出不同的幅度编码;再经DAC得到相应的阶梯波;最后经LPF对阶梯波进行平滑处理,即可得到由频率控制字决定的连续变化的输出正弦波。见图2。

DDS的输出频率fo、参考时钟频率fr、相位累加器长度N以及频率控制字K之间的关系为:

DDS的频率分频率为:

由于DDS的最大输出频率受奈斯特取样定理限制,所以fmax=f/2。

2 PLL的结构及工作原理

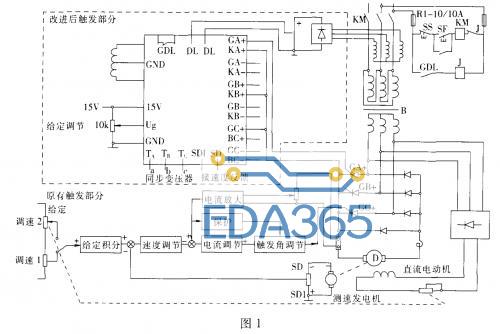

设计中通常采用数字锁相频率合成法,其基本结构由参考时钟fr、VCO(压控振荡器)、程序分频器(÷N)、PD(鉴相器)、LPF等组成。见图3。

当PLL达到稳定状态后,若输入信号为一固定频率的正弦波,则VCO的输出信号频率经程序分频器分频后与输入信号频率相等,它们之间的相位差为一常值。这种状态为环路的锁定状态。此时有:

3 基于DDS的频率合成器的设计

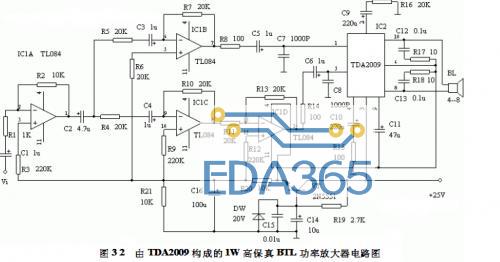

3.1 电台整机方案

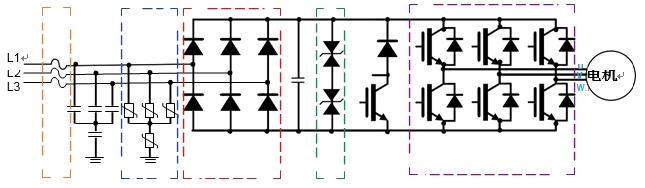

该电台工作频率范围为2 MHz~500 MHz,具有调频、调幅(包括单边带)、调相(QPSK)等功能,还可工作于跳扩频方式。在短波频段(2 MHz~30 MHz)要求调谐间隔为10 Hz,其余频段为100 Hz。设计中采用二次变频方案,第一中频取160MHz,第二中频取10.7 MHz。当然,对于160 MHz附近频段,只采用一次变频至10.7 MHz。第二中频以下采用数字化处理。简化原理框图如图4所示。

APP下载

APP下载 登录

登录

热门文章

热门文章